# **Synchronous Rectifier Controller**

### Features

- Low static VCC Current (<200uA)

- Operates in a wide output voltage range

- Self-supplying for operation with low output voltage

- Self-supplying for high-side rectification without the use of an auxiliary winding

- Supports CCM, DCM and Quasi-Resonant operations

- Supports up to 120V MOSFETs

- Ringing detection prevents false turn-on during DCM and Quasi-Resonant operations (TSR 25ns typ.)

## Description

The GR8386 is a new generation of synchronous rectifier (SR) controller ICs for switching mode power supplies. It can replace the secondary side diode for maximum efficiency at any load.

The GR8386 is a dedicated controller IC for synchronous rectification on the secondary side of flyback converters. It incorporates the SR MOSFET, which is rectifying the output of the secondary transformer winding.

The GR8386 can generate its own supply voltage for battery charging applications with low output voltage or for applications with high-side rectification.

## Applications

- Chargers

- Adapter

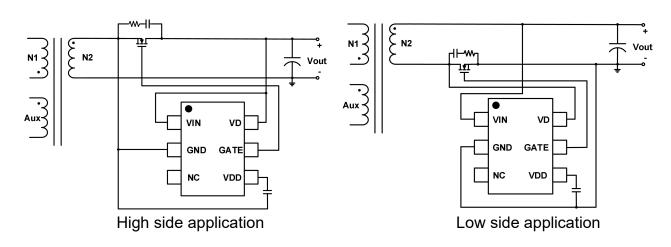

# **Typical Application Information**

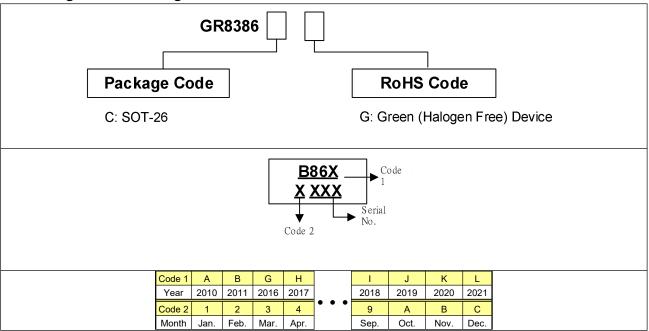

## Ordering and Marking Information

Nanjing Greenchip Semiconductor Co., Ltd. reserves the right to make changes to improve reliability or manufacture ability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

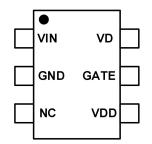

# **Pin Configuration**

## **Pin Description**

| Pin No. | Name | Function                    |  |  |  |

|---------|------|-----------------------------|--|--|--|

| 1       | VIN  | HV Linear Regulator Input   |  |  |  |

| 2       | GND  | Ground                      |  |  |  |

| 3       | NC   | No Connection               |  |  |  |

| 4       | VDD  | Internal Regulator Output.  |  |  |  |

| 5       | GATE | Gate Drive Output           |  |  |  |

| 6       | VD   | MOSFET Drain Voltage Sense. |  |  |  |

# Absolute Maximum Ratings

| VIN, VD to GND1V~ 1                                               | 30V           |

|-------------------------------------------------------------------|---------------|

| VDD, GATE                                                         | ~7V           |

| Junction temperature                                              | <b>50°</b> ℃  |

| Storage temperature range $\ $ 55 $^\circ\!\!\!\!\!\!^\circ$ ~ 15 | <b>;0 °</b> ℃ |

| SOT-26 θ <sub>JA</sub> (junction to ambient) 250 °                | с/W           |

| Lead temperature (solder) 26                                      | 30℃           |

| ESD, MM                                                           | 3KV           |

| ESD, HBM                                                          | 500V          |

**Caution:** The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed and may cause permanent damage to the IC. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the Electrical Characteristics section of the specification is not implied. The "Electrical Characteristics" table defines the conditions for actual device operation. Exposure to absolute maximum rated conditions for extended periods may affect device reliability

## **Recommended Operating Conditions**

| Item                           | Min.  | Max. | Unit |

|--------------------------------|-------|------|------|

| Operating Junction temperature | -40   | 125  | °C   |

| Operating ambient temperature  | -40   | 85   | °C   |

| VDD to GND                     | 4     | 6    | V    |

| VD to GND                      | -0.3V | 120  | V    |

| VDD Capacitor                  | 0.1   | 1    | μF   |

Note:

- Not to exceed the maximum junction temperature of the IC, this relates to the operating power of the IC and the thermal resistance of the IC-package as above.

- The small signal components should be placed close to IC pin as possible.

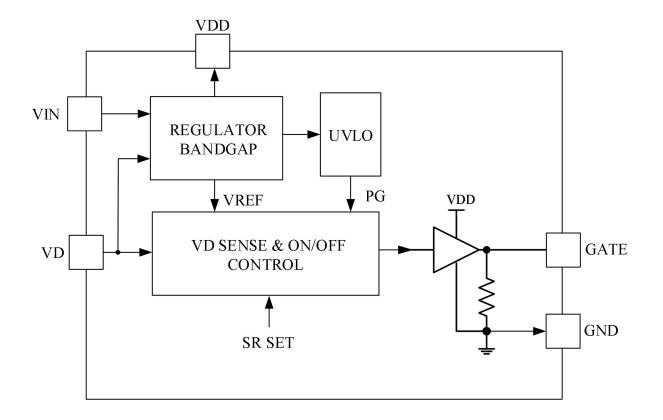

# Block Diagram

| Parameter                                         | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|------|------|------|------|

| VDD                                               |      |      |      |      |

| Start Up Current                                  |      |      | 100  | uA   |

| UVLO-ON                                           | 3.4  | 3.6  | 3.8  | V    |

| UVLO-OFF                                          | 2.8  | 3.1  | 3.3  | V    |

| VDD Operation Voltage                             |      | 5.7  |      | V    |

| Operating Current (Ivdd_op CL=2.2nF @ 100KHz)     |      | 2    | 2.5  | mA   |

| Static Current (Ivdd_st)                          |      | 200  | 300  | uA   |

| VDD Supply Current (VD=20V VDD=3V)                | 30   | 40   | 50   | mA   |

| VD                                                |      |      |      |      |

| Turn ON Threshold                                 |      | -100 |      | mV   |

| Regulation Threshold                              | -15  | -30  | -50  | mV   |

| Turn Off Threshold                                |      | 0    |      | mV   |

| Turn Off Blanking Threshold                       | 1.7  | 2    | 2.3  | V    |

| Turn Off Threshold during Tminon                  | 1.3  | 1.8  | 2.1  | V    |

| Control                                           |      |      | •    |      |

| VD Falling Slew Rate Detection (Internal setting) |      | 25   |      | ns   |

| Minimum On Time (TMINON)                          | 0.5  | 0.6  | 0.7  | us   |

| Minimum Off Time (TMINOFF)                        | 275  | 375  | 475  | ns   |

| Gate Off Propagation Delay (TGOFF)                |      | 15   | 35   | ns   |

| Maximum Off Time (TMAXOFF)                        |      | 5    |      | us   |

| Gate On Propagation Delay (TGon)                  |      | 15   | 50   | ns   |

| GATE                                              | •    | •    | •    | •    |

| Rising Time (CLoad=10nF) *                        |      | 50   |      | ns   |

| Falling Time (CLoad=10nF) *                       |      | 35   |      | ns   |

| Peak Source Current (CLoad=10nF) *                |      | 0.8  |      | Α    |

| Peak Sink Current (CLoad=10nF) *                  |      | 1.3  |      | Α    |

**Electrical Characteristics** (TA =  $+25^{\circ}$ C unless otherwise stated, VDD = 5.0V)

\*Guaranteed by Design.

## **Application Information**

#### Overview

GR8386, the secondary side driver IC, emulates the operation of diode rectifier by driving a synchronous rectifier MOSFET. Using low R<sub>DS\_ON</sub> N-MOSFET to substitute Schottky diode, the lower turn-on voltage will reduce conduction loss on rectifier. The efficiency of power converter will be boosted. The GR8386 supports operate in continuous conduction mode (CCM), discontinuous conduction mode (DCM), and QR flyback converters.

#### Under-Voltage Lockout (UVLO)

The GR8386 remains off until VDD voltage exceeds VDD turn-on threshold voltage (UVLO\_ON). Once the VDD rises above UVLO\_ON, the IC starts to work. It continues to operate until the voltage drops below UVLO turn-off threshold voltage (UVLO\_OFF).

#### **Power Supply**

Since the GR8386 VDD pin voltage can be supplied itself by charging through the 120V JFET from VD voltage. The VDD can be maintained to 5V each cycle even output voltage down to 0V.

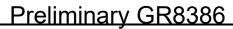

#### Gate Turn On

When the  $V_{DS}$  falling edge from 2V to on threshold -100mV is within the slew rate detection time, the gate will turn on. The slew rate detection time is internal set to around 25ns typical. The slew rate timer setting should allow normal operation and avoid from quasi-resonant ring falsely on.

#### **Gate Regulation**

When  $V_{DS}$  reaches around -30mV, the gate will be pulled to lower level to speed up the turn off phase and make sure the gate won't be turned off until the current through the SR MOSFET is nearly zero.

## Package Information

#### Gate Turn Off

When the  $V_{DS}$  reaches around 0mV, the gate will be turned off with very short delay after minimum on time blanking. If  $V_{DS}$  reaches 1.8V, the gate will be turned off immediately even within minimum on time blanking.

Fig 1. Secondary Side Operation

#### **Slew Rate Detection Function**

In DCM operations, the demagnetizing ringing may bring  $V_{DS}$  down below 0V. If Vds reaches the turn-on threshold during the ringing, SR controllers without the slew rate detection function may turn on the MOSFET by mistake. This does not only increase the power loss, but may also cause short through if the primary side FET is turned on. Considering the slew rate of the ringing is always much less than that when the primary MOSFET is really turned off, this false turn-on situation can be prevented by the slew rate detection function. When the VD slew rate is slower than the internal set threshold, the GR8386 does not turn on the gate.

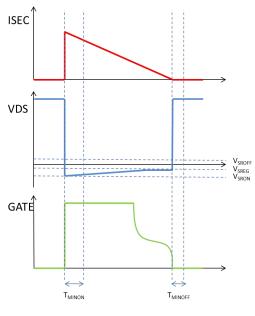

SOT-26

|        | SOT-26   |       |           |       |  |  |

|--------|----------|-------|-----------|-------|--|--|

| SYMBOL | MILLIM   | ETERS | INCHES    |       |  |  |

|        | MIN.     | MAX.  | MIN.      | MAX.  |  |  |

| А      |          | 1.45  |           | 0.057 |  |  |

| A1     | 0.00     | 0.15  | 0.000     | 0.006 |  |  |

| A2     | 0.90     | 1.30  | 0.035     | 0.051 |  |  |

| b      | 0.30     | 0.50  | 0.012     | 0.020 |  |  |

| С      | 0.08     | 0.22  | 0.003     | 0.009 |  |  |

| D      | 2.70     | 3.10  | 0.106     | 0.122 |  |  |

| E      | 2.60     | 3.00  | 0.102     | 0.118 |  |  |

| E1     | 1.40     | 1.80  | 0.055     | 0.071 |  |  |

| е      | 0.95 BSC |       | 0.037 BSC |       |  |  |

| e1     | 1.90 BSC |       | 0.075 BSC |       |  |  |

| L      | 0.30     | 0.60  | 0.012     | 0.024 |  |  |

| θ      | 0°       | 8 °   | 0°        | 8 °   |  |  |

Note: 1. Followed from JEDEC MO-178 AB.

2. Dimension D and E1 do not include mold flash, protrusions or gate burrs. Mold flash, protrusions or

gate burrs shall not exceed 10 mil per side

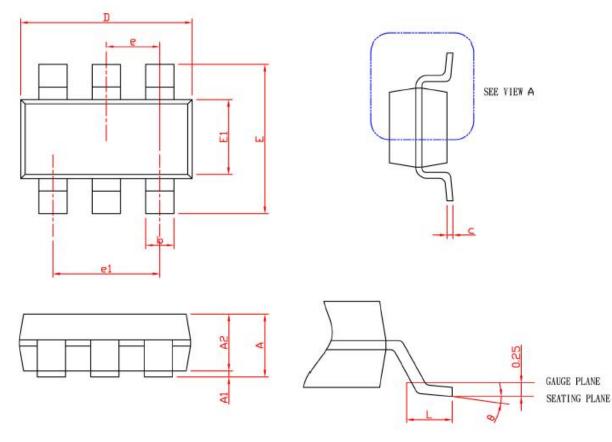

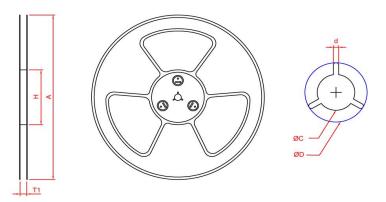

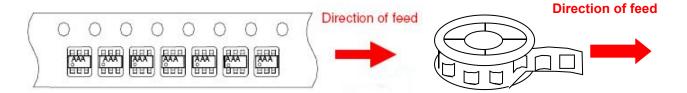

# Carrier Tape & Reel Dimensions sot-26

| Application | Α          | Н        | T1                | С                  | d        | D                 | w         | E1        | F         |

|-------------|------------|----------|-------------------|--------------------|----------|-------------------|-----------|-----------|-----------|

|             | 178.0±2.00 | 50 MIN.  | 8.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 8.0±0.30  | 1.75±0.10 | 3.5±0.05  |

| SOT-26      | P0         | P1       | P2                | D0                 | D1       | Т                 | A0        | B0        | К0        |

|             | 4.0±0.10   | 4.0±0.10 | 2.0±0.05          | 1.5+0.10<br>-0.00  | 1.0 MIN. | 0.6+0.00<br>-0.40 | 3.20±0.20 | 3.10±0.20 | 1.50±0.20 |

| Application | Carrier Width | Cover Tape Width | Devices Per Reel |

|-------------|---------------|------------------|------------------|

| SOT -26     | 8             | 5.3              | 3000             |

(mm)

Tape and Specification Reel

## **SOT 26**

Nanjing Greenchip Semiconductor Co., Ltd. reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.