# **STI8070B**

# 5A, 2.1MHz, I<sup>2</sup>C Programmable Synchronous Buck Converter with WLCSP-20 Package

# FEATURES

- Compatible I<sup>2</sup>C Interface Up to 3.4MHz

- Input Voltage Range :2.7V~5.5V

- Up to 5A Output Current

- Mode Selection Between PFM and PWM at Light Load

- Typical 50µA Quiescent Current in Light Load PFM Mode

- 2.1MHz Switching Frequency

- Integrated Soft-Start

- Input UVLO and OVP

- Build in Thermal Shutdown and OCP

- 0.25µH Inductor Support

- I<sup>2</sup>C address: 0x82

- Compact WLCSP-20 Package

# **APPLICATIONS**

- Smart Phones

- DSP or CPUs Processors

- Tablet, MID

# APPILCATIONS

# **GENERAL DESCRIPTION**

STI8070B is an I<sup>2</sup>C Programmable, high efficiency, Synchronous Buck converter that 2.1MHz. operates in wide input voltage range from 2.7V to 5.5V. The output Voltage could be programmed from 0.7125V to 1.5V. Very low standby current ensure high efficiency in light load PFM mode. The forced PWM mode could be set to avoid application problems caused by low switching frequency. A COT (Constant On-Time) structure is adaptive to achieve the fixed switching frequency and fast load transient response. STI8070B provides up to 5A output current with Integrated  $28m\Omega(high side)$  and  $18m\Omega(low side)$  power switch. STI8070B also implement an internal cycle-by-cycle soft-start and over current protection function. In addition, the input UVLO and OVP protection, Thermal shutdown protection.

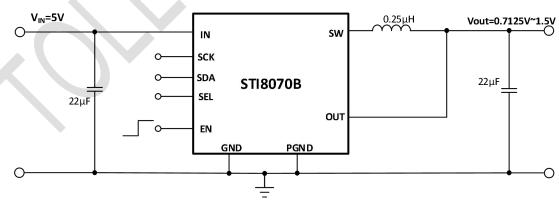

Figure 1. Basic Application Circuit

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| Parameter                              | Min  | Max | Unit |

|----------------------------------------|------|-----|------|

| All Voltage Range                      | -0.3 | 6.5 | V    |

| Junction Temperature (Note2)           | -40  | 150 | °C   |

| Storage Temperature                    | -65  | 150 | °C   |

| Junction-to-ambient Thermal Resistance | -    | 38  | °C/W |

| Junction-to-case Thermal Resistance    | -    | 9   | °C/W |

| Power Dissipation                      | -    | 2.6 | W    |

# **PACKAGE/ORDER INFORMATION**

# Top Mark: S70BXXX (S70B: Device Code, XXX: Inside Code)

| Part Number | Package  | Top mark | Quantity/ Reel |  |

|-------------|----------|----------|----------------|--|

| STI8070B    | WLCSP-20 | S70BXXX  | 3000           |  |

STI8070B devices are Pb-free and RoHS compliant.

# **PIN DESCRIPTIONS**

| Pin   | Name | Function                                                 |  |  |  |  |

|-------|------|----------------------------------------------------------|--|--|--|--|

| A1    | SEL  | Voltage select pin, 0: VSEL0 register, 1: VSEL1 register |  |  |  |  |

| A2    | EN   | Enable pin, 0: Shut down, 1: Enable                      |  |  |  |  |

| A3    | SCK  | I <sup>2</sup> C Clock pin                               |  |  |  |  |

| A4    | OUT  | Output voltage sense pin, Connect to output capacitor    |  |  |  |  |

| B1    | SDA  | I <sup>2</sup> C Data pin                                |  |  |  |  |

| B2~B3 |      |                                                          |  |  |  |  |

| C1~C4 | PGND | Power Ground pins                                        |  |  |  |  |

| B4    | AGND | Analog Ground pin                                        |  |  |  |  |

| D1~D2 | INI  | Power input nin. Connect to input conceitor              |  |  |  |  |

| E1~E2 | IN   | Power input pin, Connect to input capacitor              |  |  |  |  |

| D3~D4 | SW   | Switching Din, Connect to external Inductor              |  |  |  |  |

| E3~E4 | 300  | Switching Pin, Connect to external Inductor              |  |  |  |  |

|       | TING |                                                          |  |  |  |  |

# **ESD RATING**

| Items            | Description                   | Value | Unit |

|------------------|-------------------------------|-------|------|

| V <sub>ESD</sub> | Human Body Model for all pins | ±2000 | V    |

### **JEDEC specification JS-001**

# **RECOMMENDED OPERATING CONDITIONS**

| Items         | Description                 | Min | Max | Unit |

|---------------|-----------------------------|-----|-----|------|

| Voltage Range | IN                          | 2.7 | 5.5 | V    |

| TA            | Operating Temperature Range | -40 | 85  | °C   |

# **ELECTRICAL CHARACTERISTICS**

# ( $V_{IN}$ = 3.6V, $V_{OUT}$ = 1V, $T_A$ = 25°C, unless otherwise noted.)

| Parameter                                      | Symbol               | <b>Test Conditions</b>                                                 | Min | Тур  | Max | Unit |

|------------------------------------------------|----------------------|------------------------------------------------------------------------|-----|------|-----|------|

| Input Voltage Range                            | VIN                  |                                                                        | 2.7 |      | 5.5 | V    |

| Under Voltage Lockout                          | V <sub>UVLO</sub>    | Vin rising                                                             |     | 2.6  |     | V    |

| UVLO Hysteresis                                | VUVLO_HY             |                                                                        |     | 180  |     | mV   |

| Input OVP Voltage                              | VINOVP               | Vin rising                                                             |     | 6.15 |     | V    |

| Input OVP Hysteresis                           | V <sub>OVP_HY</sub>  |                                                                        |     | 400  |     | mV   |

| OVP blank time                                 | T <sub>OVP_BT</sub>  |                                                                        |     | 20   |     | μs   |

| Input Supply Current                           | l <sub>iN</sub>      | EN=1, I <sub>load</sub> =0,<br>V <sub>out</sub> >105%*V <sub>set</sub> |     | 50   |     | μA   |

|                                                | I <sub>SDN</sub>     | EN=0                                                                   |     | 0.1  | 1   | μA   |

| Input Shutdown current                         | I <sub>SDI2C</sub>   | I <sup>2</sup> C set shutdown,<br>EN=1                                 |     | 20   | 30  | μA   |

| EN/SDA/SCK/SEL Logic high<br>Threshold         | VINH                 |                                                                        | 1.5 |      |     | V    |

| EN/SDA/SCK/SEL Logic low                       | VINL                 |                                                                        |     |      | 0.4 | V    |

| Threshold                                      | VINL                 |                                                                        |     |      | 0.4 | v    |

| PFET peak Current limit (Note 3)               | I <sub>LIM_MAX</sub> |                                                                        | 6.7 |      |     | Α    |

| Switch On-Resistance<br>(high side) (Note 3)   | R <sub>DSONH</sub>   |                                                                        |     | 28   |     | mΩ   |

| Switch On-Resistance<br>(low side) (Note 3)    | Rdsonl               | S                                                                      |     | 18   |     | mΩ   |

| Switching Frequency                            | Fosc                 |                                                                        |     | 2.1  |     | MHz  |

| Minimum Turn-on Time                           | ton_min              |                                                                        |     | 52   |     | ns   |

| Regulator Enable to Regulated V <sub>OUT</sub> | t <sub>sst</sub>     |                                                                        |     | 300  |     | μs   |

| Thermal Shutdown Threshold<br>(Note 3)         | T <sub>SDN</sub>     | Thermal rising                                                         |     | 165  |     | °C   |

| Thermal Shutdown Hysteresis<br>(Note 3)        | T <sub>SDN_HY</sub>  |                                                                        |     | 30   |     | °C   |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:  $T_J = T_A + (P_D) \times \theta_{JA}$ .

Note 3: Thermal shutdown threshold and hysteresis are guaranteed by design.

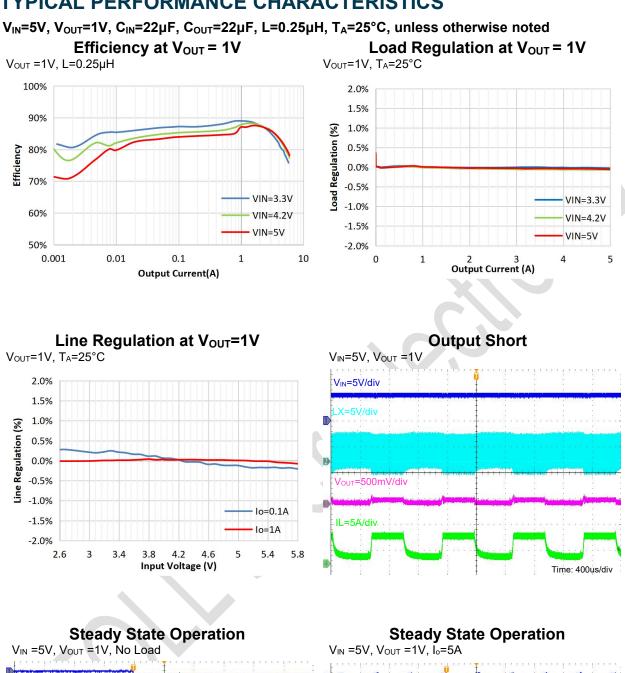

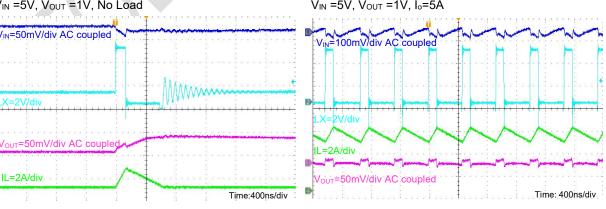

# TYPICAL PERFORMANCE CHARACTERISTICS

www.toll-semi.com

2

3

2

www.toll-semi.com

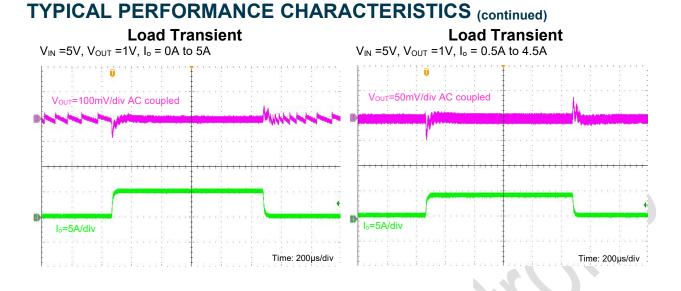

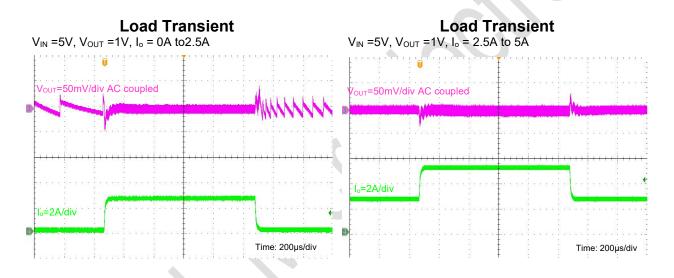

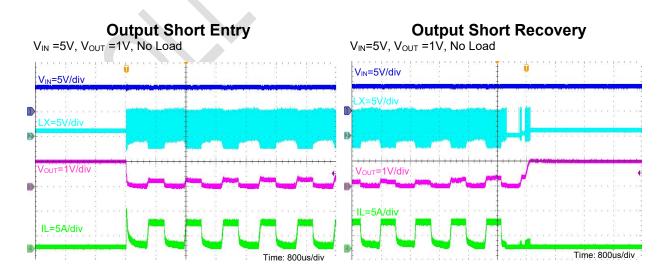

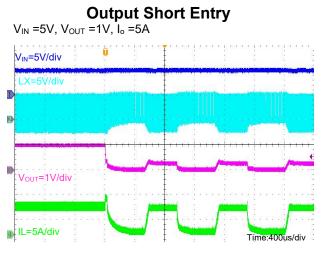

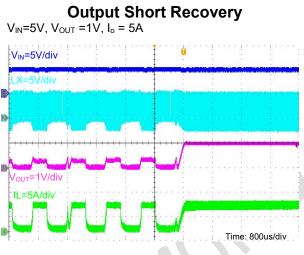

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

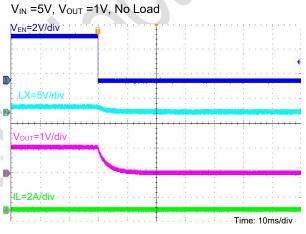

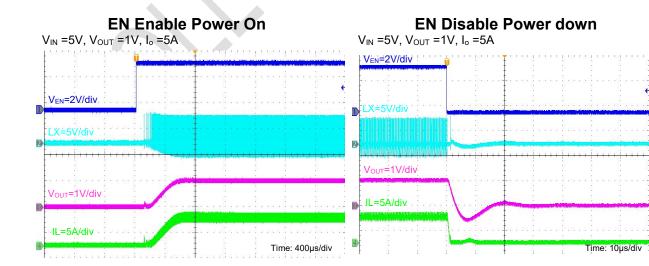

# EN Enable Power On VIN =5V, Vout =1V, No Load

### **EN Disable Power down**

# FUNCTIONAL DESCRIPTION

### Enable

EN Pin controls chip start, and STI8070B allows software to enable converter by I<sup>2</sup>C interface, BUCK EN0 and BUCK EN1 bits. The true table is showed as below.

| Piı | Pins |          | lits     |        |

|-----|------|----------|----------|--------|

| EN  | SEL  | BUCK_EN0 | BUCK_EN1 | OUTPUT |

| 0   | х    | х        | x        | OFF    |

| 1   | 0    | 0        | x        | OFF    |

| 1   | 0    | 1        | x        | ON     |

| 1   | 1    | Х        | 0        | OFF    |

| 1   | 1    | x        | 1        | ON     |

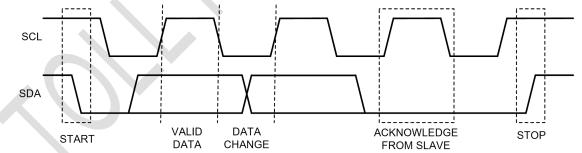

### I<sup>2</sup>C Timing

STI8070B allows the HOST to set the output voltage or other configurable function using an I<sup>2</sup>C compatible interface and STI8070B always operates as a SLAVE device. The I<sup>2</sup>C interface supports CLK frequency up to 3.4MHz and all data is transmitted with MSB(bit 7) first. In hex form, the address of STI8070B is 0x82.

STI8070B is addressed using a 7-bit address followed by a direction bit. If the direction bit is 1, the HOST reads data from STI8070B and if the direction bit is 0, the HOST writes data to STI8070B.

A transaction begins with a START condition which is a HIGH to LOW transition of the SDA line while the SCL is HIGH. A transaction ends with a STOP condition which is a LOW to HIGH transition of the SDA line while the SCL is HIGH. The data on the SDA line must stay unchanged when the SCL line is HIGH and vary only when the SCL is LOW, otherwise, STI8070B will consider it as a START or STOP condition. Each transaction contains nine clock pulses. During the ninth pulse, if the SDA line is pulled LOW by STI8070B, it is defined as an acknowledge(ACK) bit, otherwise, it is defined as an NO ACK bit.

### Write period

When the master needs to write data to STI8070B, it generates a START condition followed by the 7-bit address 0x82 and the direction bit 0, STI8070B then acknowledges by pulling SDA LOW during the ninth pulse; the master then transmits register address and the data it needs to write, the operation ends with a STOP condition.

```

www.toll-semi.com

```

### Read period

When the master needs to read data from STI8070B, it generate a START condition followed by the 7-bit address 0x82 and the direction bit 0, the master then transmit register address it needs to read from; after STI8070B acknowledges to the operation, the master issues a START condition again, followed by the 7-bit address 0x82 but the direction bit is modified to 1; the STI8070B then acknowledges and shifts out the data to the master, the master gives NO ACK and ends the operation with a STOP condition.

| S | S1AVE<br>ADDRESS+W | A   | REGISTER<br>ADDRESS | A   | S | S1AVE<br>ADDRESS+R | A | DATA     | N | Р |   |

|---|--------------------|-----|---------------------|-----|---|--------------------|---|----------|---|---|---|

|   | DRIVEN BY THE      | MAS | STER S ST           | ART | A | ACKNOWLEDGE        |   | Ś        |   |   | 5 |

|   | DRIVEN BY THE      | SL  | AVE P ST            | °0P | N | NO ACKNOWLEDG      | E | $O_{NJ}$ |   |   |   |

### I2C device Address: 0x82

### 1. VSEL0(0x00)

| Field   | Bit | R/W | Default              | Description                                                                                  |

|---------|-----|-----|----------------------|----------------------------------------------------------------------------------------------|

| BUCK_EN | 7   | R/W | 1                    | Software buck enable. When EN pin is low, the regulator is off. When EN pin is high, BUCK EN |

| 0       |     |     | bit takes precedent. |                                                                                              |

| MODEO   | 6   | R/W | 0                    | 0=Allow auto-PFM mode during light load.                                                     |

| MODE0   | 0   |     |                      | 1=Forced PWM mode                                                                            |

|         |     |     |                      | 000000 = 0.7125V                                                                             |

|         |     |     |                      | 000001 = 0.7250V                                                                             |

|         |     |     | 010111(Vout=1V)      | 000010 = 0.7375V                                                                             |

| VSEL0   | 5:0 | R/W | (0.7125+n*0.0125)    |                                                                                              |

|         |     |     | (0.7123111 0.0123)   | 010111 = 1.0000V                                                                             |

|         |     |     |                      |                                                                                              |

|         |     |     |                      | 111111 = 1.5000V                                                                             |

### 2. VSEL1(0x01)

| Field   | Bit | R/W  | Default           | Description                                    |

|---------|-----|------|-------------------|------------------------------------------------|

| BUCK EN |     |      |                   | Software buck enable. When EN pin is low, the  |

|         | 7   | R/W  | 1                 | regulator is off. When EN pin is high, BUCK_EN |

| I       |     |      |                   | bit takes precedent.                           |

| MODE1   | 6   | R/W  | 0                 | 0=Allow auto-PFM mode during light load.       |

| MODET   | 0   | r/// | 0                 | 1=Forced PWM mode                              |

|         |     |      |                   | 000000 = 0.7125V                               |

| VSEL1   | E.0 |      | 010111(Vout=1V)   | 000001 = 0.7250V                               |

| VSELI   | 5:0 | R/W  | (0.7125+n*0.0125) | 000010 = 0.7375V                               |

|         |     |      |                   |                                                |

www.toll-semi.com

# **STI8070B**

|  |  | 010111 = 1.0000V |

|--|--|------------------|

|  |  |                  |

|  |  | 111111 = 1.5000V |

### 3. Control Register(0x02)

| Field                 | Bit | R/W | Default          | Description                                          |  |

|-----------------------|-----|-----|------------------|------------------------------------------------------|--|

| Output                | 7   | R/W | 1                | 0 = discharge resistor is disabled.                  |  |

| Discharge             |     |     |                  | 1 = discharge resistor is enabled.                   |  |

|                       |     |     |                  | Set the slew rate for positive voltage transitions.  |  |

|                       |     |     |                  | 000 = 10mV/0.15µs                                    |  |

|                       |     |     |                  | 001 = 10mV/0.3µs                                     |  |

|                       |     |     | 000(10mV/0.15µs) | 010 = 10mV/0.6µs                                     |  |

| Slew Rate             | 6:4 | R/W |                  | 011 = 10mV/1.2µs                                     |  |

|                       |     |     |                  | 100 = 10mV/2.4µs                                     |  |

|                       |     |     |                  | 101 = 10mV/4.8µs                                     |  |

|                       |     |     |                  | 110 = 10mV/9.6µs                                     |  |

|                       |     |     |                  | 111 = 10mV/19.2µs                                    |  |

| reserved              | 3   | R/W | 0                | Always reads back 0                                  |  |

| Reset                 | 2   | R/W | 0                | Setting to 1 resets all registers to default values. |  |

| reserved              | 1:0 | R/W | 00               | Always reads back 0                                  |  |

| I. ID1 Register(0x03) |     |     |                  |                                                      |  |

### 4. ID1 Register(0x03)

| U        | <u> </u> | -   |         |                     |

|----------|----------|-----|---------|---------------------|

| Field    | Bit      | R/W | Default | Description         |

| VENDOR   | 7:5      | R   | 100     | IC vendor code.     |

| reserved | 4        | R   | 0       | Always reads back 0 |

| DIE_ID   | 3:0      | R   | 1000    | IC option code      |

### 5. ID2 Register(0x04)

| Field    | Bit | R/W | Default | Description           |

|----------|-----|-----|---------|-----------------------|

| reserved | 7:4 | R   | 0000    | Always Reads back 0   |

| DIE_REV  | 3:0 | R   | 0001    | IC mask revision code |

# 6. PGOOD Register(0x05)

| Field    | Bit | R/W | Default | Description                                     |

|----------|-----|-----|---------|-------------------------------------------------|

| PGOOD    | 7   | R   | 0       | 1: Buck is enabled and soft-start is completed. |

| reserved | 6:0 | R   | 000000  | Always reads back 0                             |

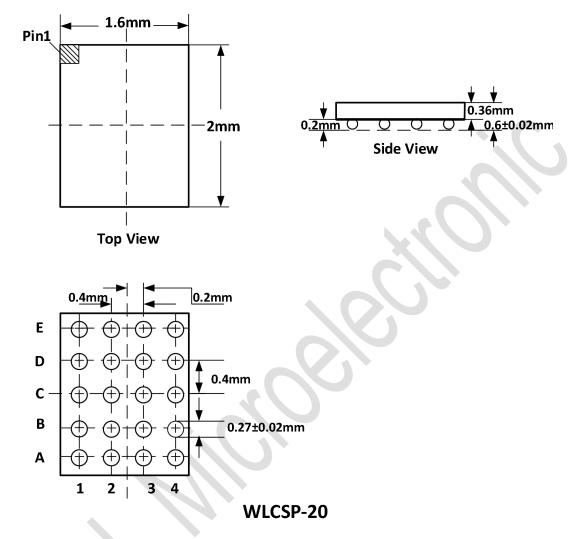

# PACKAGE INFORMATION

### WLCSP-20

### Note:

- 1) All dimensions are in millimeters.

- 2) Package length does not include mold flash, protrusion or gate burr.

- 3) Package width does not include inter lead flash or protrusion.

- 4) Lead popularity (bottom of leads after forming) shall be 0.10 millimeters max.

- 5) Pin 1 is lower left pin when reading top mark from left to right.

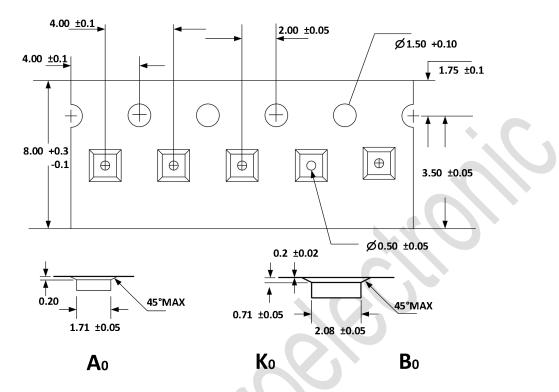

# TAPE AND REEL INFORMATION

### **TAPE DIMENSIONS: WLCSP-20**

**REEL DIMENSIONS:**

### Note:

- 1) All Dimensions are in Millimeter

- 2) Quantity of Units per Reel is 3000

- 3) MSL level is level 3.

# **Important Notification**

This document only provides product information. TOLL Microelectronic Inc. reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

TOLL Microelectronic Inc. cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a TOLL product. No circuit patent licenses are implied.

All rights are reserved by TOLL Microelectronic Inc. http:// www.toll-semi.com