### **GENERAL DESCRIPITION**

The MX16171 high-side OR-ing FET controller works with an external MOSFET and acts as an ideal diode rectifier when connected in series with the power supply. This OR-ing controller enables MOSFETs to replace diode rectifiers in power distribution networks, reducing power loss and voltage drop.

The MX16171 controller provides charge pump gate drive for an external N-channel MOSFET and fast response comparator to turn off the FET when current flows in reverse. The MX16171 can be connected to power supplies from 1V to 50V and can withstand transient voltages up to 60V.

## **FEATURES**

- ♦ Wide operating input voltage range VIN: 1V to 50V

- ♦60V transient voltage

- ♦ Charge pump gate driver for external N-channel MOSFET

- ♦ 50ns fast response to current reversal

- ♦2A peak gate off current

- ♦Ultra-small VDS turn-off voltage reduces turn-off time

- ♦ DFN3\*2-8L

## **APPLICATIONS**

Active OR-ing of redundant (N+1) power supplies

### **GENERAL INFORMATION**

### **Ordering information**

| Part Number | Description |

|-------------|-------------|

| MX16171     | DFN3*2-8L   |

| MPQ         | 3000pcs     |

### Package dissipation rating

| Package   | RθJA (°C/W) |

|-----------|-------------|

| DFN3*2-8L | 108.1       |

### **Absolute maximum ratings**

| Parameter                              | Value        |

|----------------------------------------|--------------|

| IN, OUT Pins to GND                    | -0.3 to 60V  |

| GATE Pin to GND                        | -0.3 to 60V  |

| SRC Pin to Ground                      | -0.3 to 60V  |

| EN Pin to Ground                       | -0.3 to 7V   |

| Junction temperature                   | 150°C        |

| Storage temperature, Tstg              | -50 to 150°C |

| Leading temperature (soldering,10secs) | 260°C        |

| ESD Susceptibility HBM                 | ±2000V       |

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **Recommended operating condition**

| Symbol               | Range     |

|----------------------|-----------|

| IN, OUT, SRC Pins    | 1-50V     |

| EN Pin               | 0-5.5V    |

| Junction temperature | -40~125°C |

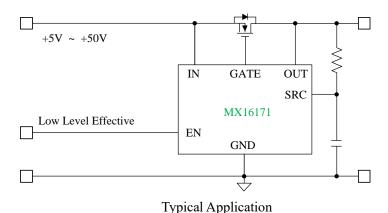

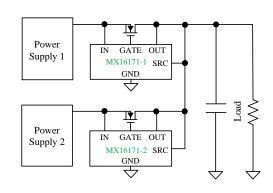

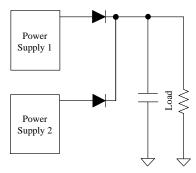

### TYPICAL APPLICATION

Typical Redundant Power Supply Configuration

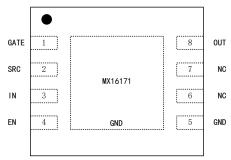

# **TERMINAL ASSIGMENTS**

Pin information

| PIN NO.     | PIN name | Description                                                                                      |

|-------------|----------|--------------------------------------------------------------------------------------------------|

| 1 GATE      |          | Connect to the Gate of the external MOSFET. Controls the MOSFET to emulate a low                 |

| 1           | GAIL     | forward- voltage diode.                                                                          |

| 2 SRC       |          | The main supply pin for all internal biasing and an auxiliary supply for the internal gate drive |

| 2           | SKC      | charge pump. Typically connected to either VOUT or VIN; a separate supply can also be used.      |

| 3           | IN       | Voltage sense connection to the external MOSFET Source pin.                                      |

|             |          | A logic high state at the EN pin will pull the GATE pin low and turn off the external MOSFET.    |

| 4           | EN       | Note that when the MOSFET is off, current will still conduct through the FET's body diode.       |

| 1           |          | This pin should may be left open or connected to GND if unused.                                  |

| 5           | GND      | Ground return for the controller                                                                 |

| 6           | NC       |                                                                                                  |

| 7           | NC       |                                                                                                  |

| 8           | OUT      | Voltage sense connection to the external MOSFET Drain pin.                                       |

| Thermal PAD | GND      | Ground return for the controller                                                                 |

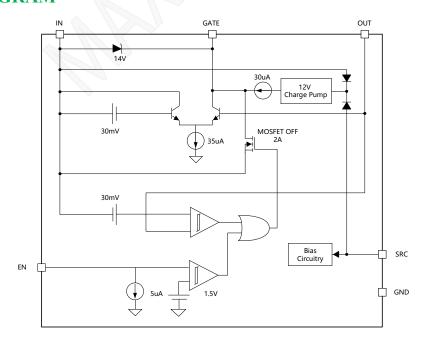

# **BLOCK DIAGRAM**

## **Electrical characteristics**

$(V_{IN}=12V,V_{SRC}=V_{IN},V_{OUT}=V_{IN},V_{EN}=0V,C_{GATE}=47nF,TA=25^{\circ}C,unless\ otherwise\ noted)$

| Symbol                 | Parameter                                                      | Test condition                                                                                                              | Min    | Тур. | Max   | Unit     |  |

|------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|------|-------|----------|--|

| SRC PIN                |                                                                |                                                                                                                             | 1 -    |      |       |          |  |

| V <sub>SRC</sub>       | Operating Supply Voltage Range                                 |                                                                                                                             | 1      | 7.5  | 50    | V        |  |

| $I_{SRC}$              | On anting Samula Comment                                       | $V_{SRC} = 5V$ , $V_{IN} = 5V$ , $V_{OUT} = V_{IN} - 100 \text{mV}$                                                         |        | 75   |       |          |  |

| 1SRC                   | Operating Supply Current                                       | $V_{SRC}$ = 12V, $V_{IN}$ = 5V, $V_{OUT}$ = $V_{IN}$ - 100mV<br>$V_{SRC}$ =60V, $V_{IN}$ = 5V, $V_{OUT}$ = $V_{IN}$ - 100mV |        | 100  |       | uA       |  |

| IN PIN                 |                                                                | VSRC-00 V, VIN - 3 V, VOUT - VIN - 100HI V                                                                                  |        | 130  |       |          |  |

| V <sub>IN</sub>        | Operating Input Voltage Range                                  |                                                                                                                             | 1      |      | 50    | V        |  |

|                        | operating input voltage range                                  | $V_{IN}=5V$ , $V_{SRC}=V_{IN}$ , $V_{OUT}=V_{IN}$ -100mV,                                                                   | •      |      | 30    | <u> </u> |  |

| 7                      |                                                                | GATE = Open                                                                                                                 |        | 190  |       | uA       |  |

| $I_{IN}$               | IN Pin current                                                 | $V_{IN} = 12V$ to 60V, $V_{SRC} = V_{IN}$ , $V_{OUT} = V_{IN}$ -                                                            |        | 220  |       |          |  |

|                        |                                                                | 100 mV, GATE = Open                                                                                                         |        | 320  |       |          |  |

| OUT PIN                |                                                                |                                                                                                                             |        |      |       |          |  |

| Vout                   | Operating Output Voltage Range                                 |                                                                                                                             | 1      |      | 50    | V        |  |

| I <sub>OUT</sub>       | OUT Pin Current                                                | $V_{IN} = 1V$ to 60V, $V_{SRC} = V_{IN}$ , $V_{OUT} = V_{IN}$ -                                                             |        | 3.2  |       | uA       |  |

|                        |                                                                | 100mV                                                                                                                       |        |      |       |          |  |

| GATE PIN               |                                                                | V -5VV -V V -V V -V                                                                                                         | 1      |      | ı     | ı        |  |

|                        |                                                                | $V_{IN} = 5V$ , $V_{SRC} = V_{IN}$ , $V_{GATE} = V_{IN}$ , $V_{OUT} = V_{IN}$ - 175mV                                       |        | 30   |       |          |  |

| I <sub>GATE(ON)</sub>  | Gate Pin Source Current                                        | $V_{IN} = 12V$ to 60V, $V_{SRC} = V_{IN}$ , $V_{GATE} = V_{IN}$                                                             |        |      |       | uA       |  |

|                        |                                                                | $V_{IN} = 12 \text{ V to 00V}, V_{SRC} = V_{IN}, V_{GATE} = V_{IN}$<br>$V_{OUT} = V_{IN} - 175 \text{mV}$                   |        | 32   |       |          |  |

| Crunhal                |                                                                | Test condition                                                                                                              | Min    | Term | Max   | Unit     |  |

| Symbol                 | Parameter                                                      | $V_{IN} = 5V$ , $V_{SRC} = V_{IN}$ , $V_{OUT} = V_{IN}$                                                                     | IVIIII | Тур. | IVIAX | Ollit    |  |

|                        |                                                                | - 175mV                                                                                                                     |        | 7    |       |          |  |

| $V_{GS}$               | $V_{\text{GATE}} - V_{\text{IN}}$ in Forward Operation         | $V_{IN} = 12V$ to 60V, $V_{SRC} = V_{IN}$ , $V_{OUT} = V_{IN}$ -                                                            |        | 10   |       | V        |  |

|                        |                                                                | 175mV                                                                                                                       |        | 12   |       |          |  |

|                        | Gate Capacitance Discharge Time                                | $C_{GATE} = 0$                                                                                                              |        | 25   | ;     |          |  |

| t <sub>GATE(REV)</sub> | at Forward to Reverse Transition                               | $C_{GATE} = 10nF$                                                                                                           |        | 60   |       | ns       |  |

|                        |                                                                | $C_{GATE} = 47nF$                                                                                                           |        | 180  |       |          |  |

| taummonn               | Gate Capacitance Discharge<br>Time at EN pin Low to High       | $C_{GATE} = 47nF$                                                                                                           |        | 486  |       |          |  |

| t <sub>GATE(OFF)</sub> | Transition                                                     | CGATE - 4/IIF                                                                                                               |        | 400  |       | ns       |  |

|                        |                                                                |                                                                                                                             |        |      | 1     |          |  |

| I <sub>GATE(OFF)</sub> | Gate Pin Sink Current                                          | $V_{GATE} = V_{IN} + 3V, V_{OUT} > V_{IN} + 100 \text{mV},$                                                                 |        | 1.8  |       | Α        |  |

|                        | Reverse V <sub>SD</sub> Threshold V <sub>IN</sub> <            | t ≤ 10ms                                                                                                                    |        |      |       |          |  |

| $V_{SD(REV)}$          | V <sub>OUT</sub>                                               | V <sub>IN</sub> - V <sub>OUT</sub>                                                                                          |        | -28  |       | mV       |  |

| $\Delta V_{SD(REV)}$   | Reverse V <sub>SD</sub> Hysteresis                             |                                                                                                                             |        | 10   |       | mV       |  |

|                        | Regulated Forward V <sub>SD</sub> Threshold                    | $V_{IN}$ =5V, $V_{SRC}$ = $V_{IN}$ , $V_{IN}$ - $V_{OUT}$                                                                   |        | 19   |       | 111 V    |  |

| V <sub>SD(REG)</sub>   | $V_{\rm IN} > V_{\rm OUT}$                                     | $V_{IN}=12V$ , $V_{SRC}=V_{IN}$ , $V_{IN}-V_{OUT}$                                                                          |        | 22   |       | mV       |  |

| EN PIN                 |                                                                |                                                                                                                             |        |      |       |          |  |

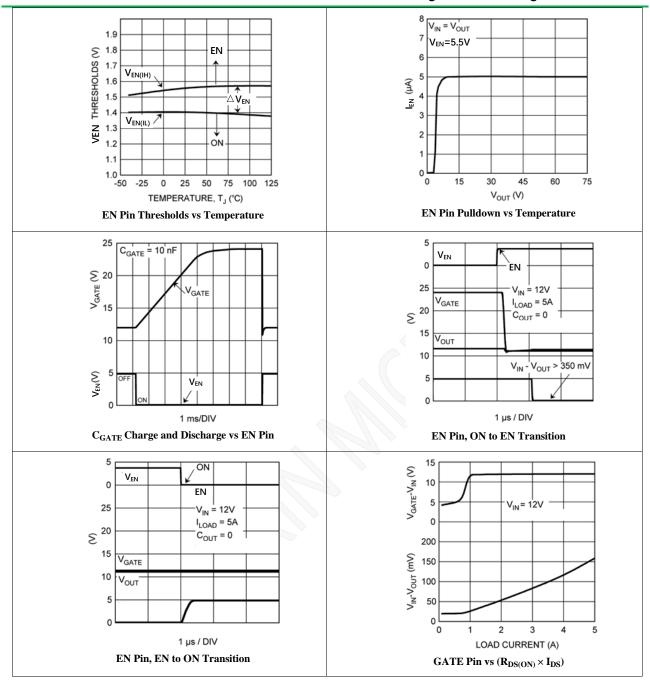

| V <sub>EN(IH)</sub>    | EN Input High Threshold Voltage                                | $V_{OUT} = V_{IN}$ - 500mV, $V_{EN}$ Rising                                                                                 |        | 1.56 |       | V        |  |

| V <sub>EN(IL)</sub>    |                                                                |                                                                                                                             |        |      |       |          |  |

|                        | EN Input Low Threshold Voltage                                 | $V_{OUT} = V_{IN}$ - 500mV, $V_{EN}$ Falling                                                                                |        | 1.4  |       |          |  |

| AV                     | <del>-</del>                                                   | $V_{OUT} = V_{IN}$ - 500mV, $V_{EN}$ Falling                                                                                |        |      |       |          |  |

| $\Delta V_{EN}$        | EN Input Low Threshold Voltage EN Threshold Voltage Hysteresis | $V_{OUT} = V_{IN} - 500 mV, V_{EN} \ Falling$ $V_{EN(IH)} - V_{EN(IL)}$                                                     |        | 1.4  |       | mV       |  |

| ΔV <sub>EN</sub>       | <del>-</del>                                                   |                                                                                                                             |        |      |       | mV       |  |

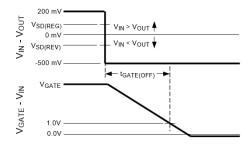

Gate OFF Timing for Forward to Reverse Transition

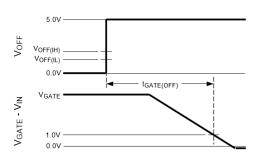

Gate OFF Timing for EN Pin Low to High Transition

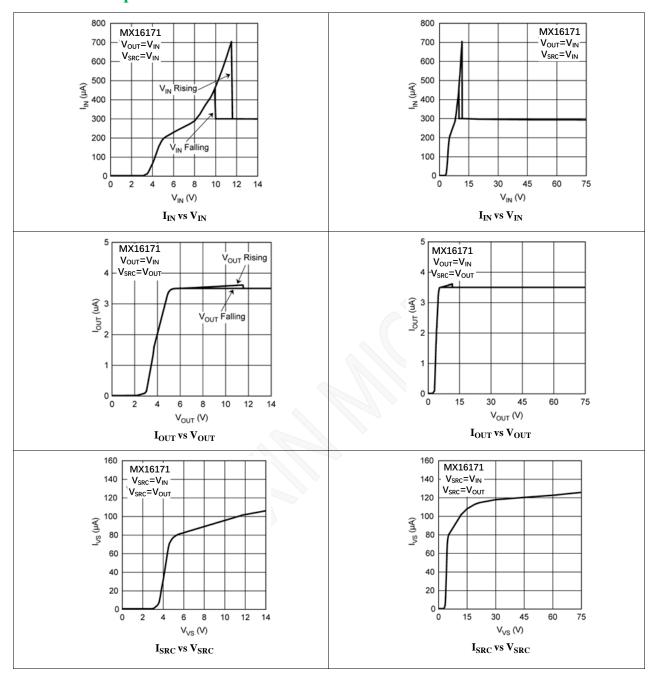

# **Characteristic plots**

# High-Side OR-ing FET Controller

# **Operation description**

### IN, GATE, and OUT Pins

When power is initially applied, the load current will flow from source to drain through the body diode of the MOSFET. Once the voltage across the body diode exceeds  $V_{\text{SD(REG)}}$  then the MX16171 begins charging the MOSFET gate through a 32  $\mu$ A (typical) charge pump current source. In forward operation, the gate of the MOSFET is charged until it reaches the clamping voltage of the 12V GATE to IN pin Zener diode internal to the MX16171.

The MX16171 is designed to regulate the MOSFET gate-to-source voltage. If the MOSFET current decreases to the point that the voltage across the MOSFET falls below the  $V_{\rm SD(REG)}$  voltage regulation point of 22mV (typical), the GATE pin voltage will be decreased until the voltage across the MOSFET is regulated at 22mV. If the source-to-drain voltage is greater than the  $V_{\rm SD(REG)}$  voltage, the gate-to-source voltage will increase and eventually reach the 12V GATE to IN pin Zener clamp level.

If the MOSFET current reverses, possibly due to failure of the input supply, such that the voltage across the MX16171 IN and OUT pins is more negative than the  $V_{\rm SD(REV)}$  voltage of -28mV (typical), the MX16171 will quickly discharge the MOSFET gate through a strong GATE to IN pin discharge transistor.

If the input supply fails abruptly, as would occur if the supply was shorted directly to ground, a reverse current will temporarily flow through the MOSFET until the gate can be fully discharged. This reverse current is sourced from the load capacitance and from the parallel connected supplies. The MX16171 responds to a voltage reversal condition typically within 25ns. The actual time required to turn off the MOSFET will depend on the charge held by the gate capacitance of the MOSFET being used. A MOSFET with 47nF of effective gate capacitance can be turned off in typically 180ns. This fast turnoff time minimizes voltage disturbances at the output, as well as the current transients from the redundant supplies.

#### **SRC Pin**

The SRC pin of MX16171 is the main supply pin for all internal biasing and an auxiliary supply for the internal gate drive charge pump.

For typical MX16171 applications, where the input voltage is above 1V, the SRC pin can be connected directly to the OUT

pin. In situations where the input voltage is close to, but not less than, the 1V minimum, it may be helpful to connect the SRC pin to the OUT pin through an RC Low-Pass filter to reduce the possibility of erratic behavior due to spurious voltage spikes that may appear on the OUT and IN pins. The series resistor value should be low enough to keep the SRC voltage drop at a minimum. A typical series resistor value is  $100\Omega$ . The capacitor value should be the lowest value that produces acceptable filtering of the voltage noise.

If SRC is powered while IN is floating or grounded, then about 0.5 mA will leak from the SRC pin into the IC and about 3mA will leak from the OUT pin into the IC. From this leakage, about 50uA will flow out of the IN pin and the rest will flow to ground. This does not affect long term reliability of the IC but may influence circuit design.

Alternately, it is possible to operate the MX16171 with VIN value as low as 1V if the SRC pin is powered from a separate supply. This separate SRC supply must be from 1V and 60V.

#### **EN Pin**

The EN pin is a logic level input pin that is used to control the gate drive to the external MOSFET. The maximum operating voltage on this pin is 5.5V.

When the EN pin is high, the MOSFET is turned off (independent of the sensed IN and OUT voltages). In this mode, load current will flow through the body diode of the MOSFET. The voltage difference between the IN pin and OUT pins will be approximately 700mV if the MOSFET is operating normally through the body diode.

The EN pin has an internal pulldown of 5  $\mu$ A (typical). If the OFF function is not required, the pin may be left open or connected to ground.

# **Application and Implementation**

## **Application Information**

Systems that require high availability often use multiple, parallel-connected redundant power supplies to improve reliability. Schottky OR-ing diodes are typically used to connect these redundant power supplies to a common point at the load. The disadvantage of using OR-ing diodes is the forward voltage drop, which reduces the available voltage and the associated power losses as load currents increase. Using an N-channel MOSFET to replace the OR-ing diode requires a small increase in the level of complexity, but reduces, or

eliminates, the need for diode heat sinks or large thermal copper area in circuit board layouts for high power applications.

OR-ing with Diodes

The MX16171 is a positive voltage (that is, high-side) OR-ing controller that will drive an external N-channel MOSFET to replace an OR-ing diode. The voltage across the MOSFET source and drain pins is monitored by the MX16171 at the IN and OUT pins, while the GATE pin drives the MOSFET to control its operation based on the monitored source-drain voltage. The resulting behavior is that of an ideal rectifier with source and drain pins of the MOSFET acting as the anode and cathode pins of a diode respectively.

**OR-ing With MOSFETs**

#### **MOSFET Selection**

The important MOSFET electrical parameters are the maximum continuous Drain current ID, the maximum Source current (that is, body diode) Is, the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the gate-to-source threshold voltage  $V_{GS(TH)}$ , the drain-to-source reverse breakdown voltage  $V_{(BR)DSS}$ , and the drain-to-source on resistance  $R_{DS(ON)}$ .

The maximum continuous drain current,  $I_D$ , rating must exceed the maximum continuous load current. The rating for the maximum current through the body diode,  $I_S$ , is typically rated the same as, or slightly higher than the drain current, but body diode current only flows while the MOSFET gate is being charged to  $V_{\rm GS(TH)}$ .

Gate Charge Time =  $Qg / I_{GATE(ON)}$

- 1. The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest differential voltage seen in the application. This would include any anticipated fault conditions.

- 2. The drain-to-source reverse breakdown voltage,  $V_{(BR)DSS}$ , may provide some transient protection to the OUT pin in low voltage applications by allowing conduction back to the IN pin during positive transients at the OUT pin.

- 3. The gate-to-source threshold voltage,  $V_{GS(TH)}$ , should be compatible with the MX16171 gate drive capabilities. Logic level MOSFETs, with  $R_{DS(ON)}$  rated at  $V_{GS(TH)}$  at 5V, are recommended, but sub-Logic level MOSFETs having  $R_{DS(ON)}$  rated at  $V_{GS(TH)}$  at 2.5V, can also be used.

- 4. The dominate MOSFET loss for the MX16171 active OR-ing controller is conduction loss due to source-to-drain current to the output load, and the R<sub>DS(ON)</sub> of the MOSFET. This conduction loss could be reduced by using a MOSFET with the lowest possible R<sub>DS(ON)</sub>. However, contrary to popular belief, arbitrarily selecting a MOSFET based solely on having low R<sub>DS(ON)</sub> may not always give desirable results for several reasons:

- 1. Reverse transition detection. Higher  $R_{DS(ON)}$  will provide increased voltage information to the MX16171 Reverse Comparator at a lower reverse current level. This will give an earlier MOSFET turnoff condition should the input voltage become shorted to ground. This will minimize any disturbance of the redundant bus.

- 2. Reverse current leakage. In cases where multiple input supplies are closely matched it may be possible for some small current to flow continuously through the MOSFET drain to source (that is, reverse) without activating the MX16171 Reverse Comparator. Higher R<sub>DS(ON)</sub> will reduce this reverse current level.

- Cost. Generally, as the R<sub>DS(ON)</sub> rating goes lower, the cost of the MOSFET goes higher.

- 5. The dominate MOSFET loss for the MX16171 active OR-ing controller is conduction loss due to source-to- drain current to the output load, and the R<sub>DS(ON)</sub> of the MOSFET. This conduction loss could be reduced by using a MOSFET with the lowest possible R<sub>DS(ON)</sub>. However, contrary to popular belief, arbitrarily selecting a MOSFET based solely on having low R<sub>DS(ON)</sub> may not always give desirable results for several

reasons:

- a. Selecting a MOSFET with an  $R_{DS(ON)}$  that is too large will result in excessive power dissipation. Additionally, the MOSFET gate will be charged to the full value that the MX16171 can provide as it attempts to drive the Drain to Source voltage down to the  $V_{SD(REG)}$  of 22mV typical. This increased Gate charge will require some finite amount of additional discharge time when the MOSFET needs to be turned off.

- b. As a guideline, it is suggested that  $R_{\rm DS(ON)}$  be selected to provide at least 22mV, and no more than 100mV, at the nominal load current.

- c.  $(22mV / I_D) \le R_{DS(ON)} \le (100mV / I_D)$

- d. The thermal resistance of the MOSFET package should also be considered against the anticipated dissipation in the MOSFET to ensure that the junction temperature  $(T_J)$  is reasonably well controlled, because the  $R_{DS(ON)}$  of the MOSFET increases as the junction temperature increases.

- 6.  $P_{DISS} = I_D^2 \times (R_{DS(ON)})$

- 7. Operating with a maximum ambient temperature  $(T_{A(MAX)})$  of 35°C, a load current of 10 A, and an  $R_{DS(ON)}$  of 10 m $\Omega$ , and desiring to keep the junction temperature under 100°C, the maximum junction-to-ambient thermal resistance rating  $(\theta_{JA})$  must be:

- a.  $R_{\theta JA} \le (T_{J(MAX)} T_{A(MAX)}) / (I_D^2 \times R_{DS(ON)})$

- b.  $R_{\theta JA} \le (100^{\circ}C 35^{\circ}C) / (10A \times 10A \times 0.01\Omega)$

- c.  $R_{\theta JA} \le 65^{\circ}C/W$

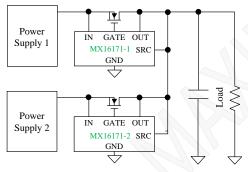

### **Short Circuit Failure of an Input Supply**

An abrupt  $0\Omega$  short circuit across the input supply will cause the highest possible reverse current to flow while the internal MX16171 control circuitry discharges the gate of the MOSFET. During this time, the reverse current is limited only by the  $R_{DS(ON)}$  of the MOSFET, along with parasitic wiring resistances and inductances. Worst case instantaneous reverse current would be limited to:

$$I_{D(REV)} = (V_{OUT} - V_{IN}) / R_{DS(ON)}$$

(1)

The internal Reverse Comparator will react, and will start the process of discharging the Gate, when the reverse current reaches:

$$I_{D(REV)} = V_{SD(REV)} / R_{DS(ON)}$$

(2)

When the MOSFET is finally switched off, the energy stored in the parasitic wiring inductances will be transferred to the rest of the circuit. As a result, the MX16171 IN pin will see a negative voltage spike while the OUT pin will see a positive voltage spike. The IN pin can be protected by diode clamping the pin to GND in the negative direction. The OUT pin can be protected with a TVS protection diode, a local bypass capacitor, or both. In low voltage applications, the MOSFET drain to-source breakdown voltage rating may be adequate to protect the OUT pin (that is,  $V_{IN} + V_{(BR)DSS(MAX)} < 60V$ ), but most MOSFET data sheets do not ensure the maximum breakdown rating, so this method should be used with caution.

Reverse Recovery Current Generates Inductive Spikes at  $V_{\rm IN}$  and  $V_{\rm OUT}$  pins

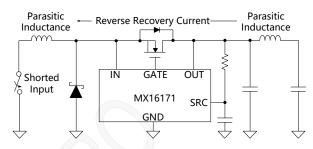

# **Package information**

NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN

AND 0.25MM FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

| SYMBOL | MILLIMETERS |      |      |  |

|--------|-------------|------|------|--|

| STMBOL | MIN         | NOM  | MAX  |  |

| A      | 0.45        |      | 0.55 |  |

| A1     | 0           |      | 0.05 |  |

| A3     |             | 0.13 |      |  |

| b      | 0.2         |      | 0.3  |  |

| D      |             | 2    |      |  |

| D2     | 1.35        |      | 1.45 |  |

| Е      |             | 3    |      |  |

| E2     | 1.25        |      | 1.35 |  |

| e      |             | 0.5  |      |  |

| L      | 0.25        |      | 0.35 |  |

| L1     |             |      | 0.15 |  |

## **Restrictions on Product Use**

- ♦ MAXIN micro is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing MAXIN products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such MAXIN products could cause loss of human life, bodily injury or damage to property.

- ◆ In developing your designs, please ensure that MAXIN products are used within specified operating ranges as set forth in the most recent MAXIN products specifications.

- ◆ The information contained herein is subject to change without notice.

Version update record:

V10 The original version (preliminary)