# 2A/18V/340kHz Synchronous Buck Converter

# **General Description**

The VP2128 is an efficiency and low-cost synchronous step-down converter with integrated low  $R_{\text{DS(ON)}}$  high-side  $150m\Omega/\text{low-side}$   $130m\Omega$  MOSFET switch. It is capable of delivering 2A continuous output current over a wide range of supplying voltage from 4.75V to 18V. With a simple voltage divider, the output voltage is easily adjustable from 0.922V to 16V.

Other features such as 340kHz PWM frequency, programmable soft-start, OCP protection and low 50µA shutdown current/ 1.2mA quiescent current make VP2128 ideally to be used in application like communication equipments and networking devices.

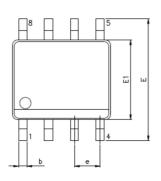

The VP2128 is available in popular SO-8P green package with exposed pad.

## **Features**

- 4.75V to 18V Input Voltage Range

- Adjustable Output from 0.922V to 16V

- Continuous 2A Output Current

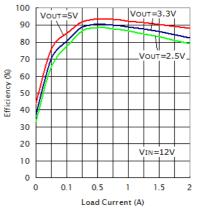

- 93% Conversion Efficiency at 5V/1A Output

- Integrated Boot-Diode

- Integrated 150mΩ/130mΩ MOSFET Switches

- Low 50µA Shutdown Current

- Low 1.2mA Quiescent Current

- Fixed 340kHz Switching Frequency

- Adapted Current Mode PWM Operation

- Programmable Soft-Start Function

- Over Voltage and Current Limit

- Over Temperature Protection

- RoHS 2.0 compliant SO-8P Green Package with Exposed Pad

# **Applications**

- Wireless Communication Device

- Networking Device

- Set-Top Box

- LCD Monitor/ LCD TV

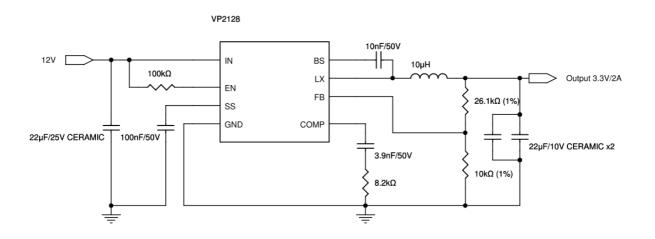

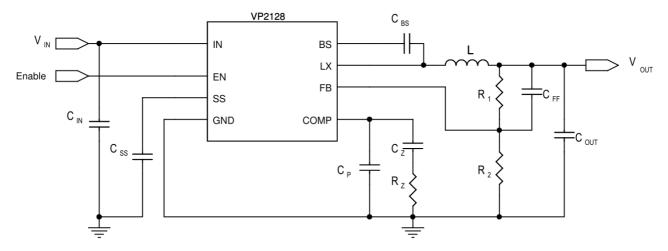

# **Typical Application**

1

# **Functional Block Diagram**

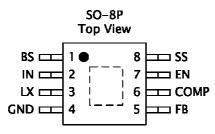

# **Pin Assignments And Descriptions**

| Pin No. | Pin        | I/O/P | Function Description                                                      |

|---------|------------|-------|---------------------------------------------------------------------------|

|         |            |       | High-Side N Channel MOSFET Gate drive boost input. Connect at least       |

| 1       | 1 BS       |       | 10nF capacitor from LX to BS to control the High-Side switch. Place the   |

|         |            |       | capacitor close to this pin if possible.                                  |

| 2       | IN         | Р     | Power Input. Drive IN with a 4.75V to 18V power source to activate the    |

| 2       | IIN        | r     | converter.                                                                |

| 3       | LX         | 0     | Power Switching Output. LX is the switching node that supplies power      |

| 3       |            |       | to the output.                                                            |

| 4       | GND        | Р     | Power ground.                                                             |

| 5       | FB         | ı     | Feedback Input. FB monitors the output voltage to regulate that volt-     |

| )       | 3   18   1 |       | age. Use a voltage divider feedback from the output to drive FB pin.      |

|         |            |       | Compensation Node. COMP is used to compensate the regulation con-         |

| 6       | COMP       |       | trol loop. Connect a series RC network from COMP to GND to compen-        |

|         | COMP       | _     | sate the regulation control loop. In some cases, an additional capacitor  |

|         |            |       | from COMP to GND is also permitted.                                       |

| 7       | EN         | ı     | Chip Enable. Pull EN high to enable the converter, pull it low to turn it |

| /       | LIN        |       | off. Pull up with a $100k\Omega$ resistor to start it up automatically.   |

|         |            |       | Soft-Start Control. SS controls the soft-start time. A 100nF capacitor    |

| 8       | SS -       | _     | sets the soft-start time to 15ms typically. Leave it floating would make  |

|         |            |       | soft-start time become very short.                                        |

# **Absolutely Maximum Ratings**

Over operating free-air temperature range, unless otherwise specified (\* 1)

| Symbol                             | Parameter                             | Limit                        | Unit |

|------------------------------------|---------------------------------------|------------------------------|------|

| V <sub>IN</sub>                    | Supply voltage range                  | -0.3 to 20                   | V    |

| $V_{LX}$                           | Switch voltage range                  | -1 to V <sub>IN</sub> +0.3   | V    |

| V <sub>BS</sub>                    | High side gate drive voltage range    | $V_{LX}$ -0.3 to $V_{LX}$ +6 | ٧    |

| V <sub>IN</sub> (COMP, EN, FB, SS) | Low voltage input range               | -0.3 to 6                    | V    |

| T <sub>J</sub>                     | Operating junction temperature range  | -40 to +160                  | ۰C   |

| T <sub>STG</sub>                   | Storage temperature range             | -65 to 150                   | ۰C   |

| Electrostatic discharge            | Human body model                      | ±2                           | kV   |

| Electrostatic discharge            | Machine model                         | ±200                         | V    |

| θјς                                | Thermal Resistance (Junction to Case) | 10                           | °C/W |

| $\theta_{JA}$                      | Thermal Resistance (Junction to Air)  | 50                           | °C/W |

<sup>(\*1):</sup> Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

# **Recommended Operating Conditions**

| Symbol           | Parameter                            | Specif | Unit |      |

|------------------|--------------------------------------|--------|------|------|

| Symbol           | i didilictei                         | Min    | Max  | Onic |

| V <sub>IN</sub>  | Supply voltage                       | 4.75   | 18   | V    |

| V <sub>out</sub> | Output voltage                       | 0.922  | 16   | V    |

| T <sub>A</sub>   | Operating free-air temperature range | -40    | 85   | ۰C   |

# **Electrical Characteristics**

$T_A=25^{\circ}\!C,\,V_{IN}=12V,\,unless$  otherwise noted

| Symbol               | Parameter                                   | Test Condition                           | Sp  | Specification |       |      |

|----------------------|---------------------------------------------|------------------------------------------|-----|---------------|-------|------|

| Symbol               | Parameter                                   | rest Condition                           | Min | Тур           | Max   | Unit |

| $I_{SD}$             | Shutdown supply current                     | $V_{EN} = 0V$                            |     | 50            |       | μΑ   |

| IQ                   | Supply current                              | V <sub>EN</sub> =2.0V, Non-<br>Switching |     | 1.2           |       | mA   |

| $V_{UVLO}$           | Under voltage lockout                       |                                          |     | 4.7           |       | V    |

| $V_{REF}$            | Reference voltage                           | $4.75V \le V_{IN} \le 18V$               | 0.9 | 0.922         | 0.946 | V    |

| $R_{\text{DS(ON)H}}$ | High–Side switch R <sub>DS(ON)</sub>        |                                          |     | 150           |       | mΩ   |

| $R_{DS(ON)L}$        | Low-Side switch R <sub>DS(ON)</sub>         |                                          |     | 130           |       | mΩ   |

| I <sub>LKH</sub>     | High–Switch leakage current                 | $V_{EN}$ =0V, $V_{LX}$ =0V               |     |               | 1     | μΑ   |

|                      | Current limit                               |                                          |     | 4.1           |       | Α    |

| $A_{EA}$             | Error amplifier voltage gain                |                                          |     | 480           |       | V/V  |

| $G_{EA}$             | Error amplifier transconductance            | ΔI <sub>C</sub> =±10μA                   |     | 800           |       | μ℧   |

| Gcs                  | COMP to current sense transconduct-<br>ance |                                          |     | 4             |       | Ω    |

| $f_{OSC}$            | Oscillation frequency                       |                                          |     | 340           |       | kHz  |

| $f_{OSC-SH}$         | Short circuit oscillation frequency         | $V_{FB} = 0V$                            |     | 100           |       | kHz  |

| $D_{MAX}$            | Maximum duty cycle                          | $V_{FB} = 0.8V$                          |     | 90            |       | %    |

| t <sub>ON(min)</sub> | Minimum ON time                             |                                          |     | 200           |       | ns   |

|                      | EN shutdown threshold voltage               | V <sub>EN</sub> rising                   |     | 1.5           |       | V    |

|                      | EN input low current                        |                                          |     | 0.1           |       | μΑ   |

|                      | Soft-Start time                             | $C_{SS} = 100nF$                         |     | 15            |       | ms   |

|                      | Thermal shutdown threshold                  |                                          |     | 150           |       | ۰C   |

|                      | Thermal shutdown hysteresis                 |                                          |     | 20            |       | ۰C   |

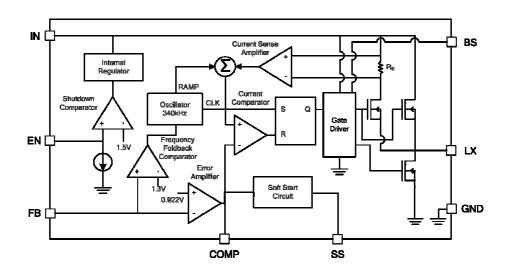

## **Functional Descriptions**

The VP2128 is a fixed frequency, current mode asynchronous buck converter. During normal operation, the internal MOSFET switch is controlled by the gate driver and dominates the duty cycle of the PWM waveform. While the switch is turned off, the inductor current flows through the external diode.

## **PWM Oscillation**

The frequency of the internal oscillator is fixed at 340kHz. In case of short circuit (output/feedback voltage is zero), the frequency will be down to 100kHz to reduce the heat and minimize the power consumption.

## **Error Amplifier**

The error amplifier compares the voltage of FB pin with the internal voltage reference  $V_{\text{REF}}$ . When the output current increases, the voltage of FB pin decreases and the error amplifier output will start to increase. This will force the gate driver to increase the duty cycle of the PWM waveform and raise the inductor current to compensate the output voltage drop.

#### Soft-Start

The VP2128 is capable of the soft-start function to avoid inrush current and prevent output voltage from overshooting during start-up period.

# Chip Enable

The VP2128 has an EN pin to perform chip enable control. The regulator can be enabled and disabled by simply applying state logic values on EN pin. The precision values of the rising threshold is 1V and the falling threshold is 0.8V. Never leave the EN pin floating and make sure the value of the logic away from the voltage region of rising threshold and falling threshold.

# Under-voltage Lockout

Under-voltage lockout (UVLO) is implemented to protect the internal gate driver away from uncertain state and lose the control of the MOSFET switch. UVLO threshold voltage is 4.7V typically.

#### Thermal Protection

Thermal shutdown is implemented to prevent the chip from operating at exceedingly high temperatures. When the silicon die temperature is higher than its upper threshold, it forces the whole chip entering shutdown state. When the temperature is lower than its lower threshold, it resumes the normal operation.

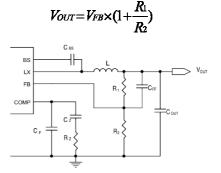

## **Output Voltage**

In Figure 1, the output voltage can be set by the resistor network connected to the output voltage terminal and FB pin. The resistor network divides the output voltage down to the feedback voltage by the follow ratio:

$$V_{FB} = V_{OUT} \frac{R_2}{R_1 + R_2}$$

where  $V_{FB}$  is the feedback voltage,  $V_{OUT}$  is the output voltage.

Thus the output voltage can be obtained by the following equation:

Figure 1. Output network of VP2128

# **Application Information**

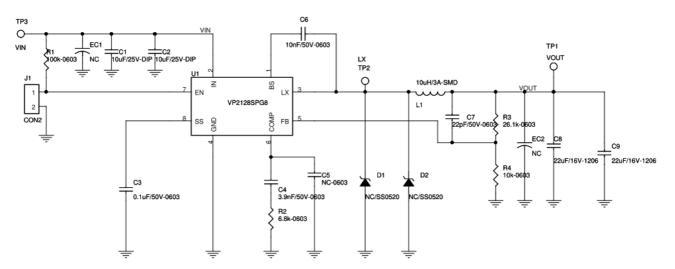

Figure 2. VP2128 typical application

## Input Supply Voltage

$V_{\text{IN}}$  supplies current to internal control circuits and output voltages. The supply voltage range is from 4.75V to 18V. A power on reset (POR) continuously monitors the input supply voltage. The buck converter draws pulsed current with sharp edges each time the upper switch turns on, resulting in voltage ripples and spikes at supply input. A minimum  $22\mu F$  ceramic capacitor with shortest PCB trace is highly recommended for bypassing the supply input.

| V <sub>IN</sub> | 1.2V                                                                       | 1.8V                                                                          | 2.5V                                                                                                                   | 3.3V                                                                         | 5V                                                                           | 9V                                                                            |

|-----------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 9V              | $\begin{array}{l} L:3.3\mu H \\ R_1:3k\Omega \\ R_2:10k\Omega \end{array}$ | $\begin{array}{l} L:3.3\mu H \\ R_1:9.53k\Omega \\ R_2:10k\Omega \end{array}$ | $\begin{array}{c} \text{L:}6.8\mu\text{H} \\ \text{R}_1\text{:}16.9k\Omega \\ \text{R}_2\text{:}10k\Omega \end{array}$ | $\begin{array}{l} L:10\mu H \\ R_1:26.1k\Omega \\ R_2:10k\Omega \end{array}$ | $\begin{array}{l} L:15\mu H \\ R_1:45.3k\Omega \\ R_2:10k\Omega \end{array}$ |                                                                               |

| 12V             | $\begin{array}{l} L:3.3\mu H \\ R_1:3k\Omega \\ R_2:10k\Omega \end{array}$ | $\begin{array}{l} L:3.3\mu H \\ R_1:9.53k\Omega \\ R_2:10k\Omega \end{array}$ | $\begin{array}{c} \text{L:}6.8\mu\text{H} \\ \text{R}_1\text{:}16.9k\Omega \\ \text{R}_2\text{:}10k\Omega \end{array}$ | $\begin{array}{l} L:10\mu H \\ R_1:26.1k\Omega \\ R_2:10k\Omega \end{array}$ | $\begin{array}{l} L:15\mu H \\ R_1:45.3k\Omega \\ R_2:10k\Omega \end{array}$ | L:15 $\mu$ H<br>R <sub>1</sub> :59 $k\Omega$<br>R <sub>2</sub> :6.8 $k\Omega$ |

Table 1. R1/R2 Ratio vs. Output voltage

#### Output Voltage

The output voltage can be set by the resistor network connected to the output voltage terminal and FB pin. The resistor network divides the output voltage down to the feedback voltage by the follow ratio:

$$V_{FB} = V_{OUT} \frac{R_2}{R_1 + R_2}$$

where  $V_{FB}$  is the feedback voltage,  $V_{OUT}$  is the output voltage.

Thus the output voltage can be obtained by the following equation:

$$V_{OUT} = 0.922 \frac{R_1 + R_2}{R_2}$$

Applying the feed-forward capacitor ( $C_{FF}$ ) could improve the frequency jitter of the output PWM waveform caused by the improper layout criteria. With good layout the capacitor should not be added. If the value of  $C_{FF}$  is too large (>1nF), this capacitor will be almost transparent for lower frequency of spikes from output voltage and these noise could disturb the operation of the internal gate driver. The value of  $C_{FF}$  shall be lower than 1nF.

#### Soft-Start

The VP2128 features programmable soft-start function to avoid the in-rush current from supply input. Soft-start capacitor shall be connected to SS pin as capacitor  $C_{SS}$  shown in Figure 2. Once the converter exits UVLO state or shutdown mode, such scheme will ramp up the output voltage slowly. It can be used to program the output volt-

age ramp speed by changing the value of the capacitor. For one 100nF soft-start capacitor, the soft-start period is 15ms typically.

## Input Under Voltage Lockout

When the VP2128 is powered on and EN pin is also held high, the internal circuit will remain inactive until  $V_{\text{IN}}$  exceeds the input UVLO threshold voltage. This function assures the converter works properly and protects the internal gate driver away from entering any unexpected state.

#### **Short Circuit Protection**

Once the output is shorted to ground, the protection circuit will be activated and the oscillation frequency will be reduced to lower frequency around 100kHz to prevent the inductor current increasing beyond the current limit. The PWM frequency will be back to its typical value 340kHz after the short condition is removed.

## **Over Temperature Protection**

The VP2128 integrates the circuits to protect itself away from overheating. When junction temperature of the output driver reaches to threshold point like 160°C, the converter will enter the shutdown state and LX pin would be high impedance. The converter will resume only when the driver junction temperature drops more than 20°C from overheating threshold temperature.

#### **Loop Compensation**

The VP2128 employs current mode control to simplify the compensation and improve transient response. The loop stability and transient response are controlled through the COMP pin. The COMP pin is the output of the internal transconductance error amplifier.

Select the appropriate compensation value by following procedure:

1. Calculate the  $R_Z$  value with the following equation:

$$Rz < \frac{2\pi \times Cout \times 0.1 \times f}{G_{EA} \times G_{CS}} \times \frac{Vout}{V_{FB}}$$

2. Calculate the  $C_z$  value with the following equation:

$$Cz < \frac{4}{2\pi \times Rz \times 0.1 \times f}$$

3. Determine if the second compensation capacitor C<sub>P</sub> is required. It is required if the ESR zero of the output capacitor is located at less than half of the switching frequency, or the following relationship holds:

$$\frac{1}{2\pi \times C_Z \times R_{ESR}} < \frac{f}{2}$$

Thus, the value of  $C_P$  can be calculated with the following equation:

$$C_P = \frac{C_Z \times R_{ESR}}{R_Z}$$

Determining  $R_Z$  and  $C_Z$  could be tedious steps. To simplify the calculation, a quick reference table contains  $R_Z$  and  $C_Z$  is listed below on Table 2. Although the factor of layout style is not considered, this table could be general to approach the optimal compensation network.

| V <sub>OUT</sub> | 1.2V  | 1.8V  | 2.5V  | 3.3V  | 5V    | 9V     |

|------------------|-------|-------|-------|-------|-------|--------|

| Rz               | 3kΩ   | 3kΩ   | 6.8kΩ | 8.2kΩ | 13kΩ  | 26.1kΩ |

| Cz               | 3.9nF | 3.9nF | 3.9nF | 3.9nF | 3.9nF | 3.9nF  |

Table 2. Recommended value of Rz and Cz

#### **Inductor Selection**

7

The value of the inductor affects the ripples of output voltage and must be carefully selected. In the same working condition, larger inductance value results in lower output ripple voltage but such inductor will be oversized, higher series resistance and lower saturation current. In most

cases, it would be a good rule to keep peak-to-peak switching current  $\Delta I_L$  to be approximate 30% of the maximum switching current. And it is necessary to assure the peak inductor current is under maximum switch current limit. Thus, the inductance can be calculated by the following equation:

$$L = \frac{V_{OUT}}{f \times \Delta I_L} (1 - \frac{V_{OUT}}{V_{IN}})$$

where f is the switch frequency, L is the inductance.

Hence the maximum peak current limit of the inductor  $I_{L(PEAK)}$  can be obtained by:

$$I_{L(PEAK)} = I_{LOAD} + \Delta I_{L} = \frac{V_{OUT}}{2 f \times L} (1 - \frac{V_{OUT}}{V_{IN}})$$

where ILOAD is the maximum load current.

With the equations listed above, the inductance of inductor can be calculated easily. Actually, the selection of the inductor is the compromise of the cost, size and desired electro-magnetic compatibility.

## Input Capacitor (C<sub>IN</sub>) Selection

The VP2128 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. A ceramic capacitor about  $22\mu F$  is recommended for the decoupling capacitor. An additional  $0.1\mu F$  speed-up capacitor near pin 2 to ground is good to provide additional high noise filtering. The capacitor voltage rating needs to be greater than the maximum input voltage.

# Output Capacitor (Cout) Selection

The output capacitor is required to stabilize the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. If non-Low ESR electrolytic capacitors are used, limit the total value of the  $C_{OUT}$  lower than  $470\mu F$ . Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{I_{LOAD}}{f \times L} (1 - \frac{V_{OUT}}{V_{IN}}) (R_{ESR} + \frac{1}{8 \times f \times C_{OUT}})$$

Where  $C_{\text{OUT}}$  is the output capacitance value and  $R_{\text{ESR}}$  is the equivalent series resistance (ESR) value of the output capacitor. In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f^2 \times L \times C_{OUT}} (1 - \frac{V_{OUT}}{V_{IN}})$$

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f \times L} (1 - \frac{V_{OUT}}{V_{IN}}) R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The VP2128 can be optimized for a wide range of capacitance and ESR values.

## **Boot-Strap Capacitor Selection**

A 10nF ceramic capacitor must be connected between the BS pin to LX pin for proper operation. It is recommended to use a ceramic capacitor.

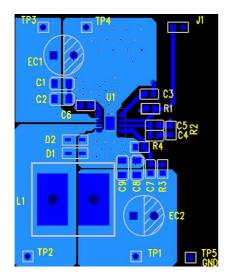

#### **PCB Layout Guidelines**

- 1. Keep the input switching current loop as small as possible.

- 2. Keep the LX pin as physically small and short as possible to minimize parasitic capacitance and inductance and to minimize radiated emissions.

- 3. Keep analog and non-switching components away from switching components.

- 4. Do not allow switching current to flow under the device.

- 5. Output capacitor should be connected to a broad pattern of the GND.

- 6. Voltage feedback loop should be as short as possible, and preferably with ground shield.

- 7. Extra via is preferable for IN, LX and GND connection.

- 8.  $C_{IN}$  / $C_{OUT}$  should be placed as near as possible to the device.

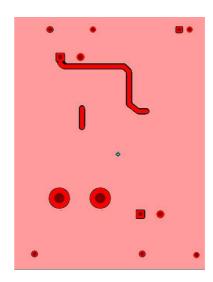

Figure 3. VP2128 reference evaluation board layout

Figure 4. VP2128 reference evaluation board schematic

# **Typical Characteristics**

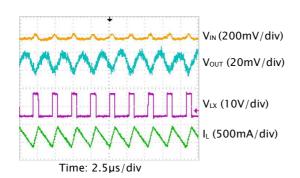

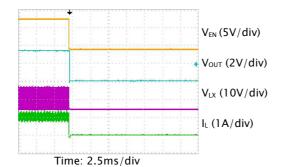

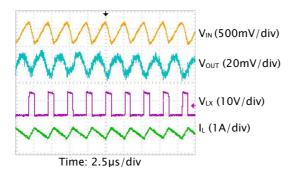

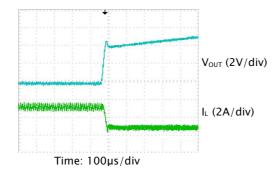

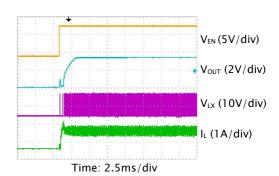

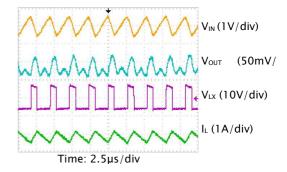

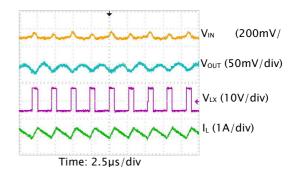

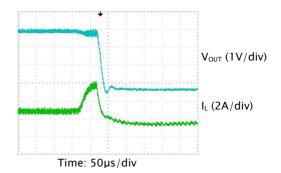

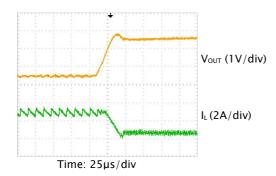

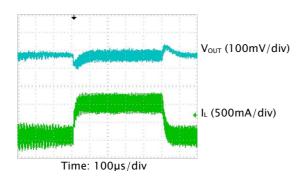

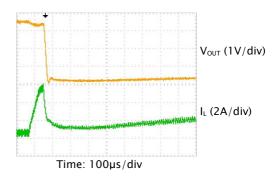

$T_A = 25 ^{\circ}\text{C}, \ V_{IN} = 12 \text{V}, \ V_{OUT} = 3.3 \text{V}, \ Inductor = 10 \mu\text{H}, \ C_{IN} = 10 \mu\text{F}, \ C_{OUT} = 22 \mu\text{F}, \ unless \ otherwise \ noted.}$

Figure 5. Steady State Operation

Figure 7. Shutdown Through Enable

Figure 9. Medium Load (1A) Operation

Figure 11. Heavy Load (2A) Short Circuit Recovery

Figure 6. Start-Up Through Enable

Figure 8. Heavy Load (2A) Operation

Figure 10. Light Load (no load) Operation

Figure 12. Heavy Load (2A) Short Circuit Protection

# **Typical Characteristics (cont.)**

Figure 13. Light Load (no load) Short Circuit Recovery

Figure 15. Load Transient

Figure 14. Light Load (no load) Short Circuit Protection

Figure 16. Efficiency

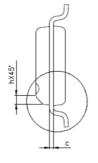

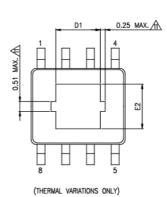

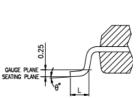

# **Package Information**

#### SO-8P

| D     | ı             |

|-------|---------------|

| 40.10 | SEATING PLANE |

| Sym- | Stan     | dard | Thermal  |      |  |

|------|----------|------|----------|------|--|

| bols | Min.     | Max. | Min.     | Max. |  |

| Α    | -        | 1.75 | -        | 1.70 |  |

| A1   | 0.10     | 0.25 | 0.00     | 0.15 |  |

| A2   | 1.25     | -    | 1.25     | -    |  |

| b    | 0.31     | 0.51 | 0.31     | 0.51 |  |

| С    | 0.10     | 0.25 | 0.10     | 0.25 |  |

| D    | 4.90 BSC |      | 4.90 BSC |      |  |

| E    | 6.00     | BSC  | 6.00 BSC |      |  |

| E1   | 3.90 BSC |      | 3.90     | BSC  |  |

| е    | 1.27 BSC |      | 1.27 BSC |      |  |

| L    | 0.40     | 1.27 | 0.40     | 1.27 |  |

| h    | 0.25     | 0.50 | 0.25     | 0.50 |  |

| θ°   | 0        | 8    | 0        | 8    |  |

#### **Thermal Enhanced Dimensions**

| Pad Size | E    | 2    | D1   |      |  |

|----------|------|------|------|------|--|

| Pau Size | Min. | Max. | Min. | Max. |  |

| 90x90E   | 1.94 | 2.29 | 1.94 | 2.29 |  |

| 95x13E   | 2.05 | 2.41 | 2.81 | 3.30 |  |

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target.

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification. TYP: Typical. Provided as a general value. This value is not a device specification.

2. Dimensions in Millimeters.

JEDEC Outline: MS-012 AA Rev. F (Standard), MS-012 BA Rev. F (Thermal)

Dimensions "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions and gate burrs shall not exceed 0.51mm per side.

5. Dimensions "E1" does not include inter-lead flash, or protrusions. Inter-lead flash and protrusions shall not exceed 0.25mm per side.

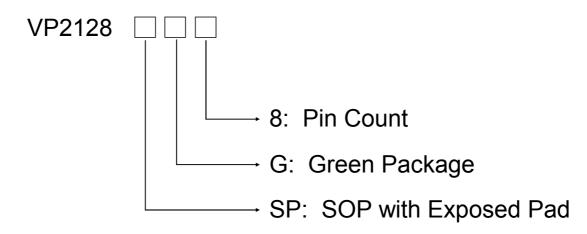

# **Ordering Information**

| Part No.   | Q`ty/Reel |

|------------|-----------|

| VP2128SPG8 | 2,500     |

## **Contact Information**

## **Viva Electronics Incorporated**

10F-1, No. 32, Gaotie 2nd Rd., Zhubei City, Hsinchu County, Taiwan, R.O.C.

Tel: 886-3-6579508 Fax: 886-3-6579509

WWW: http://www.viva-elec.com.tw

#### **IMPORTANT NOTICE**

Viva Electronics Incorporated reserves the right to make changes without further notice to any products or specifications herein. Viva Electronics Incorporated does not assume any responsibility for use of any its products for any particular purpose, nor does Viva Electronics Incorporated assume any liability arising out of the application or use of any its products or circuits. Viva Electronics Incorporated does not convey any license under its patent rights or other rights nor the rights of others.