## PART NUMBER 54F151B2A-ROCA

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# 8-Input Data Selector/Multiplexer

### ELECTRICALLY TESTED PER: MIL-M-38510/33901

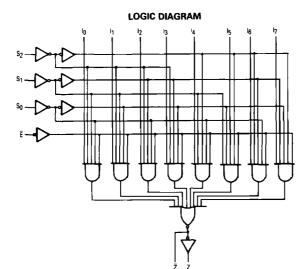

The 54F151 is a high-speed 8-input digital multiplexer. It provides in one package, the ability to select one line of data from up to eight sources. The 'F151 can be used as a universal function generator to generate any logic function of four variables. Both asserted and negated outputs are provided.

The 'F151 is a logic implementation of a single pole, 8-position switch with the switch position controlled by the state of the three Select inputs,  $S_0$ ,  $S_1$ ,  $S_2$ . The Enable input ( $\overline{E}$ ) is active LOW. The logic function provided at the output is:

$$Z = \overline{E} \cdot ([0 \cdot \overline{S}_0 \cdot \overline{S}_1 \cdot \overline{S}_2 + I_1 \cdot \underline{S}_0 \cdot \overline{S}_1 \cdot \overline{S}_2 + I_2 \cdot \overline{S}_0 \cdot \underline{S}_1 \cdot \overline{S}_2 + I_3 \cdot \underline{S}_0 \cdot \underline{S}_1 \cdot \overline{S}_2 + I_4 \cdot \overline{S}_0 \cdot \overline{S}_1 \cdot \underline{S}_2 + I_5 \cdot \underline{S}_0 \cdot \overline{S}_1 \cdot \underline{S}_2 + I_6 \cdot \overline{S}_0 \cdot \underline{S}_1 \cdot \underline{S}_2 + I_7 \cdot \underline{S}_0 \cdot \underline{S}_1 \cdot \underline{S}_2)$$

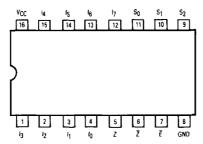

#### **CONNECTION DIAGRAM**

### Military 54F151

#### AVAILABLE AS:

1) JAN: JM38510/33901BXA

2) SMD: \*

3) 883C: 54F151/BXAJC

X = CASE OUTLINE AS FOLLOWS:

PACKAGE: CERDIP: E

CERFLAT: F

\*Call Factory for latest update

#### PIN ASSIGNMENTS

| FUNCTION                         | DIL | FLATS | LCC | BURN-IN<br>(CONDITION A |

|----------------------------------|-----|-------|-----|-------------------------|

| 13                               | 1   | 1     | 2   | VCC                     |

| 13<br>1 <sub>2</sub>             | 2   | 2     | 3   | Vcc                     |

| 11                               | 3   | 3     | 4   | VCC                     |

|                                  | 4   | 4     | 5   | VCC                     |

| ž                                | 5   | 5     | 7   | OPEN                    |

| lo<br>Z<br>Ž                     | 6   | 6     | 8   | OPEN                    |

| Ē                                | 7   | 7     | 9   | VCC                     |

| GND                              | 8   | 8     | 10  | GND                     |

| <b>S</b> <sub>2</sub>            | 9   | 9     | 12  | VCC                     |

| S <sub>1</sub>                   | 10  | 10    | 13  | VCC                     |

| S <sub>1</sub><br>S <sub>0</sub> | 11  | 11    | 14  | VCC                     |

| 17                               | 12  | 12    | 15  | Vcc                     |

| 16                               | 13  | 13    | 17  | VCC                     |

| 15                               | 14  | 14    | 18  | VCC                     |

| l <u>å</u>                       | 15  | 15    | 19  | VCC                     |

| VCC                              | 16  | 16    | 20  | VCC                     |

BURN-IN CONDITIONS: V<sub>CC</sub> = 5.0 V MIN/6.0 V MAX

Table 1

| Test Type        | S1     |

|------------------|--------|

| tPLH             | open   |

| tpHL.            | apen   |

| tPHZ             | open   |

| <sup>t</sup> PZH | open   |

| tPLZ             | closed |

| tPZL             | closed |

54F151

| TRUTH TABLE |                |                |                |                |               |  |  |

|-------------|----------------|----------------|----------------|----------------|---------------|--|--|

|             | Inp            | Outputs        |                |                |               |  |  |

| Ē           | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Ž              | Z             |  |  |

| Н           | Х              | ×              | ×              | н              | L             |  |  |

| L           | L              | L              | Ł              | Ĩο             | 10            |  |  |

| L           | L              | L              | н              | Ī <sub>1</sub> | Ιĭ            |  |  |

| L           | L              | Н              | L              | Ī2             | l2            |  |  |

| L           | L              | н              | н              | Ĭз             | la            |  |  |

| L           | н              | L              | L              | Ī3<br>Ī4       | 14            |  |  |

| L           | н              | L              | Н              | Ī5             | 3<br> 4<br> 5 |  |  |

| L           | Н              | н              | Ļ              | Ī <sub>6</sub> | 16            |  |  |

| L           | н              | н              | н              | 17             | 17            |  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

#### 54F151

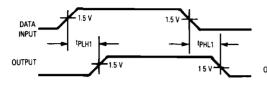

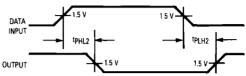

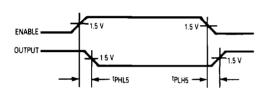

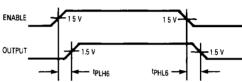

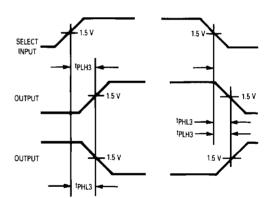

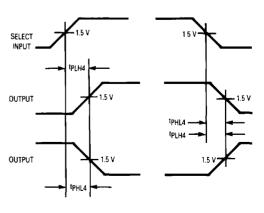

#### **WAVEFORMS**

#### NOTES:

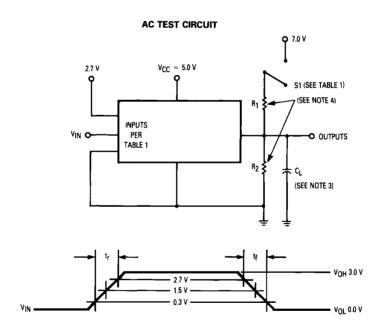

- **NOTES:**1. V<sub>IN</sub> = Input pulse and has the following characteristics: PRR  $\leq$  1.0 MHz, t<sub>T</sub> = t<sub>T</sub>  $\leq$  2.5 ns, Z<sub>Out</sub>  $\approx$  50  $\Omega$ .

2. Terminal conditions (pins not designated may be high  $\approx$  2.0 V, low  $\leq$  0.8 V, or open.

3. C<sub>L</sub> = 50 pF  $\pm$  10% including scope probe, wiring and stray capacitance, without package in test fixture.

4. R<sub>1</sub> = R<sub>2</sub> = 499  $\Omega$   $\pm$  5.0%.

5. Voltage measurements are to be made with respect to network ground terminal.

#### 54F151

| Symbol | mbol Parameter Limits           |            |          |             |       | Units       | Test Condition (Unless Otherwise Specified) |    |                                                                                                                                                                                                                 |

|--------|---------------------------------|------------|----------|-------------|-------|-------------|---------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                 | +2         | 25°C + 1 |             | 25°C  | - 55°C      |                                             |    | _                                                                                                                                                                                                               |

|        | Static<br>Parameters:           | Subgroup 1 |          | Subgroup 2  |       | Subgroup 3  |                                             |    |                                                                                                                                                                                                                 |

|        |                                 | Min        | Max      | Min         | Max   | Min         | Max                                         |    |                                                                                                                                                                                                                 |

| Vон    | Logical "1"<br>Output Voltage   | 2.5        |          | 2.5         | i     | 2.5         |                                             | v  | $ \begin{array}{l} V_{CC} = 4.5 \ \text{V, I}_{OH} = -1.0 \ \text{mA,} \\ V_{IL} = 0.8 \ \text{V, S} = 0.8 \ \text{V or } 2.0 \ \text{V,} \\ \overline{E} = 2.0 \ \text{V or } 0.8 \ \text{V.} \\ \end{array} $ |

| VOL    | Logical "0"<br>Output Voltage   |            | 0.5      |             | 0.5   |             | 0.5                                         | ٧  | $V_{CC} = 4.5 \text{ V}, I_{OL} = 20 \text{ mA}, V_{IH} = 2.0 \text{ V},$<br>S = 0.8 V or 2.0 V, $\overline{E} = 0.8 \text{ V}.$                                                                                |

| VIC    | Input Clamping<br>Voltage       |            | - 1.2    |             |       |             |                                             | ٧  | V <sub>CC</sub> = 4.5 V, I <sub>IN</sub> = -18 mA, other inputs are open.                                                                                                                                       |

| ΙΉ     | Logical "1"<br>Input Current    |            | 20       |             | 20    |             | 20                                          | μΑ | V <sub>CC</sub> = 5.5 V, V <sub>IH</sub> = 2.7 V,<br>other inputs are open, $\tilde{E}$ = 4.5 V or<br>(2.7 V), S = 0 V, 4.5 V or (2.7 V).                                                                       |

| ηнн    | Logical "1"<br>Input Current    |            | 100      |             | 100   |             | 100                                         | μА | V <sub>CC</sub> = 5.5 V, V <sub>IHH</sub> = 7.0 V,<br>other inputs are open, $\vec{E}$ = 4.5 V or<br>(7.0 V), S = 0 V, 4.5 V or (7.0 V).                                                                        |

| lir.   | Logical "0"<br>Input Current    | - 0.03     | -0.6     | - 0.03      | 0.6   | -0.03       | -0.6                                        | mA | $V_{CC} = 5.5 \text{ V}, V_{ N} = 0.5 \text{ V},$<br>other inputs are open, $\vec{E} = 0 \text{ V}$ or $(0.5 \text{ V})$<br>S = 4.5  V, 0  V or $(0.5  V)$ .                                                    |

| lOD    | Diode Current                   | 60         |          | 60          |       | 60          |                                             | mA | $V_{CC}=4.5$ V, other inputs are open, $S=0$ V, $V_{IN}=5.5$ V, $V_{OUT}=2.5$ V, $E=5.5$ V or 0 V.                                                                                                              |

| los    | Short Circuit<br>Output Current | - 60       | - 150    | - 60        | - 150 | - 60        | - 150                                       | mA | $V_{CC} = 5.5 \text{ V}$ , $V_{IN} = 4.5 \text{ V}$ , all other inputs are open, $V_{OUT} = 0 \text{ V}$ , $S = 0 \text{ V}$ , $\overline{E} = 0 \text{ V}$ .                                                   |

| Icc    | Power Supply<br>Current         |            | 21       |             | 21    |             | 21                                          | mA | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 4.5 V (all inputs).                                                                                                                                                  |

| VIH    | Logical "1"<br>Input Voltage    | 2.0        |          | 2.0         |       | 2.0         |                                             | ٧  | V <sub>CC</sub> = 4.5 V.                                                                                                                                                                                        |

| VIL    | Logical "0"<br>Input Voltage    |            | 0.8      |             | 0.8   |             | 0.8                                         | ٧  | V <sub>CC</sub> = 4.5 V.                                                                                                                                                                                        |

|        |                                 | Subgroup 7 |          | Subgroup 8A |       | Subgroup 8B |                                             |    |                                                                                                                                                                                                                 |

|        | Functional Tests                |            |          |             |       |             |                                             |    | per Truth Table with $V_{CC}=4.5$ V, (Repeat at), $V_{CC}=5.5$ V, $V_{IL}=0.5$ V, and $V_{IH}=2.5$ V.                                                                                                           |

#### 54F151

| Symbol            | Limits                                                   |            |         |            |       |            | Units | Test Condition (Unless Otherwise Specified) |                                                                            |

|-------------------|----------------------------------------------------------|------------|---------|------------|-------|------------|-------|---------------------------------------------|----------------------------------------------------------------------------|

|                   | +25°C                                                    |            | + 125°C |            | -55°C |            |       |                                             |                                                                            |

|                   | Switching<br>Parameters                                  | Subgroup 1 |         | Subgroup 2 |       | Subgroup 3 |       |                                             |                                                                            |

|                   | Min                                                      | Max        | Min     | Max        | Min   | Max        | 1     |                                             |                                                                            |

| <sup>t</sup> PHL1 | Propagation Delay<br>/Data-Output<br>In to Z             | 3.7        | 7.0     | 3.5        | 9.0   | 3.5        | 9.0   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| <sup>t</sup> PLH1 | Propagation Delay<br>/Data-Output<br>In to Z             | 3.0        | 6.5     | 2.5        | 8.5   | 2.5        | 8.5   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| <sup>†</sup> PHL2 | Propagation Delay<br>/Data-Output<br>In to Z             | 1.5        | 4.0     | 1.5        | 6.0   | 1.5        | 6.0   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| <sup>t</sup> PLH2 | Propagation Delay /Data-Output In to Z                   | 3.0        | 6.5     | 2.5        | 7.5   | 2.5        | 7.5   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,} $ $R_1 = R_2 = 499 \Omega.$ |

| <sup>t</sup> PHL3 | Propagation Delay<br>/Data-Output<br>S <sub>n</sub> to Z | 4.0        | 9.0     | 4.0        | 9.5   | 4.0        | 9.5   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| <sup>t</sup> PLH3 | Propagation Delay<br>/Data-Output<br>S <sub>n</sub> to Z | 4.5        | 13      | 4.5        | 13.5  | 4.5        | 13.5  | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,} $ $R_1 = R_2 = 499 \Omega.$ |

| <sup>†</sup> PHL4 | Propagation Delay<br>/Data-Output<br>S <sub>n</sub> to Z | 3.2        | 7.5     | 3.0        | 8.0   | 3.0        | 8.0   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,} $ $R_1 = R_2 = 499 \Omega.$ |

| <sup>t</sup> PLH4 | Propagation Delay<br>/Data-Output<br>Sn to Z             | 4.0        | 9.0     | 3.5        | 11.5  | 3.5        | 11.5  | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,} $ $R_1 = R_2 = 499 \Omega.$ |

| <sup>t</sup> PHL5 | Propagation Delay<br>/Data-Output<br>E to Z              | 3.5        | 7.0     | 3.0        | 8.0   | 3.0        | 8.0   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| <sup>†</sup> PLH5 | Propagation Delay<br>/Data-Output<br>E to Z              | 5.0        | 9.5     | 4.0        | 12    | 4.0        | 12    | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| <sup>t</sup> PHL6 | Propagation Delay<br>/Data-Output<br>E to Z              | 3.0        | 6.0     | 2.5        | 6.5   | 2.5        | 6.5   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |

| tPLH6             | Propagation Delay<br>/Data-Output<br>E to Z              | 3.0        | 6.1     | 3.0        | 7.5   | 3.0        | 7.5   | ns                                          | $V_{CC} = 5.0 \text{ V, } C_L = 50 \text{ pF,}$ $R_1 = R_2 = 499 \Omega.$  |